- 快召唤伙伴们来围观吧

- 微博 QQ QQ空间 贴吧

- 视频嵌入链接 文档嵌入链接

- 复制

- 微信扫一扫分享

- 已成功复制到剪贴板

Flow and HQoS DPDK Acceleration Using 100GBE Intel Programmable Acceleration

展开查看详情

1 . x Flow and HQoS Acceleration Over DPDK Using Intel Programmable Acceleration Card N3000 ROSEN XU, SANTOS CHEN INTEL

2 .Agenda • Key Hardware Features • DPDK and OPAE • A Typical Flow and HQoS Acceleration Reference Design • HQoS Acceleration • Flow and HQoS Acceleration in DPDK • Future work 2

3 .Key Hardware Features ► Intel® Arria® 10 GT1150 8x10GbE , 4x25GbE Network Interfaces Local DDR4 and QDR Memory ► Dual Intel® Ethernet Controller XL710 Extensive OS support and Easier system integration XL710 enable and XL710 bypass ► PCIe Interface 2 x PCIe Gen3x8 host interface 2xPCIe Gen3x8 towards the FPGA PCIe Gen3x8 towards each of the XL710 PCIe SMBus connected MAX10 and all XL710 ► Intel® MAX® 10 CPLD Board power, clocks and reset control Board security and management 3

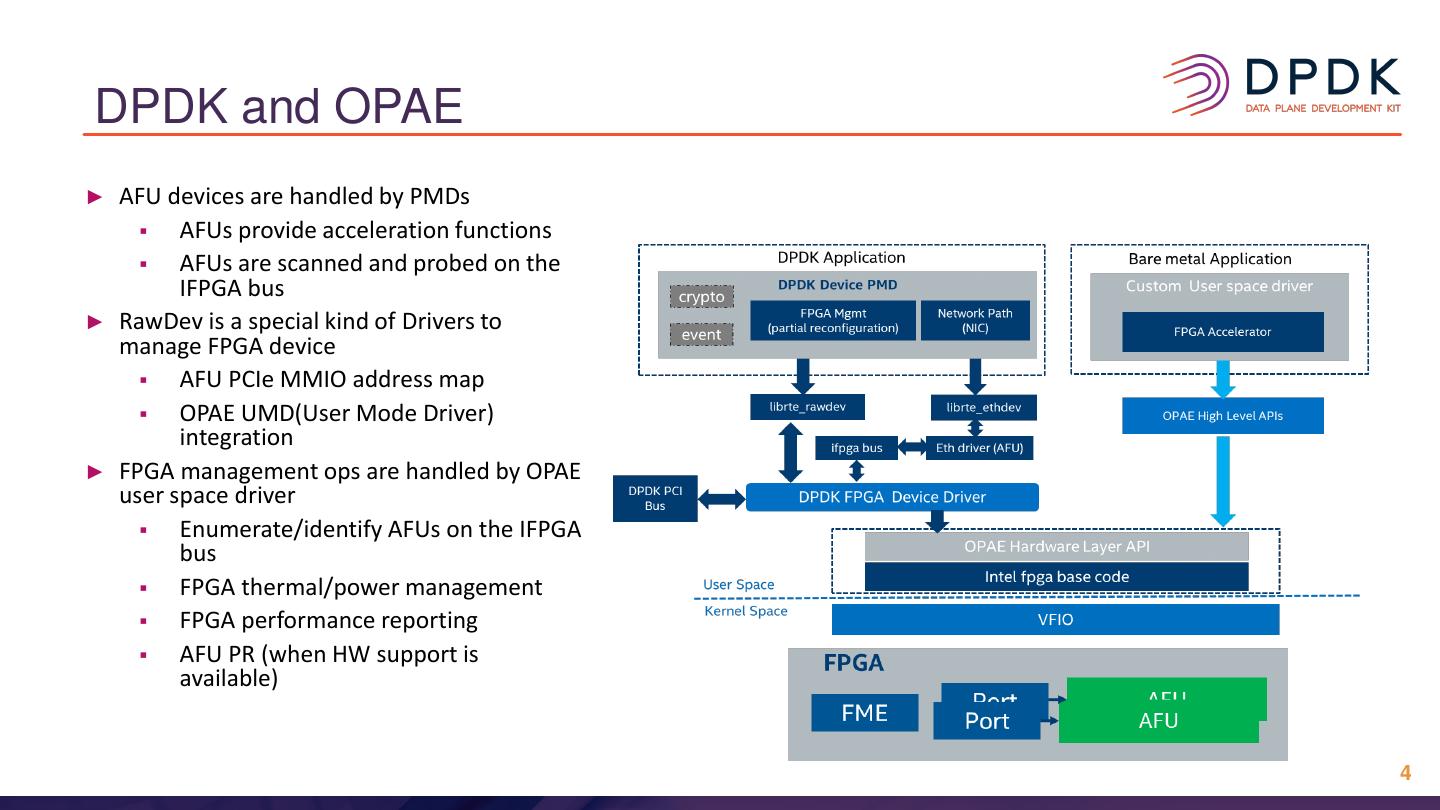

4 .DPDK and OPAE ► AFU devices are handled by PMDs AFUs provide acceleration functions AFUs are scanned and probed on the IFPGA bus ► RawDev is a special kind of Drivers to manage FPGA device AFU PCIe MMIO address map OPAE UMD(User Mode Driver) integration ► FPGA management ops are handled by OPAE user space driver Enumerate/identify AFUs on the IFPGA bus FPGA thermal/power management FPGA performance reporting AFU PR (when HW support is available) 4

5 .A Typical Flow and HQoS Acc. Reference Design DPDK APP EGRESS INGRESS TX PIPELINE PIPELINE RX Table STAGE STAGE Configuration Packet and Metadata FPGA PCIe XL710 PCIe Classifica Flow Parser FDIR/RSS Line tion Lookup NIC Packet Packet etc Side Side And MAC MAC Queue ID MAC Metadata Modifica HQoS Extractio tion n ► Ingress Flow Partial Offload ► Egress Flow Based HQoS Flow search data in metadata Flow is identified by Queue ID DPDK parse metadata ► DPDK Pipeline Handle other Packet Processing 5

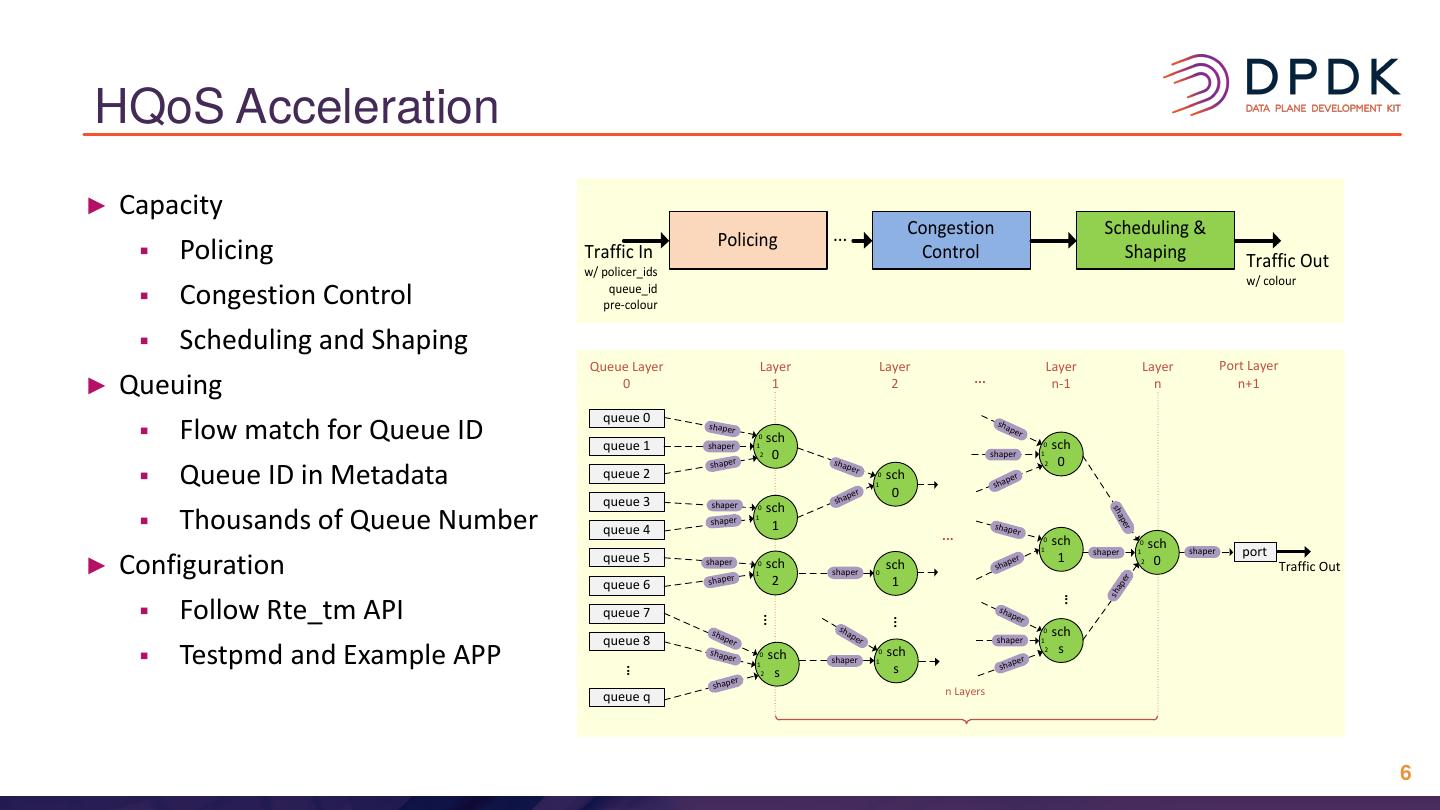

6 .HQoS Acceleration ► Capacity ... Congestion Scheduling & Policing Policing Traffic In Control Shaping Traffic Out w/ policer_ids w/ colour Congestion Control queue_id pre-colour Scheduling and Shaping Queue Layer Layer Layer Layer Layer Port Layer ► Queuing 0 1 2 ... n-1 n n+1 queue 0 Flow match for Queue ID shaper sh a per 0 sch queue 1 shaper 1 0 sch 2 0 shaper 1 shaper s h ap 2 0 Queue ID in Metadata er queue 2 0 sch per 1 sh a ap e r 0 queue 3 shaper 0 sch sh Thousands of Queue Number sh a 1 shaper pe queue 4 1 s h ap e r r ... sch 0 0 sch 1 shaper 1 shaper port ► queue 5 1 Configuration shaper shaper 1 0 sch 2 shaper 0 sch 1 sh ap e r 2 0 Traffic Out er queue 6 ap sh ... Follow Rte_tm API queue 7 sh a per ... ... sh a sh a 0 sch per pe queue 8 r shaper 1 Testpmd and Example APP s h ap e 0 sch 0 sch 2 s r shaper 1 er 1 s s h ap ... r 2 s s h ap e n Layers queue q 6

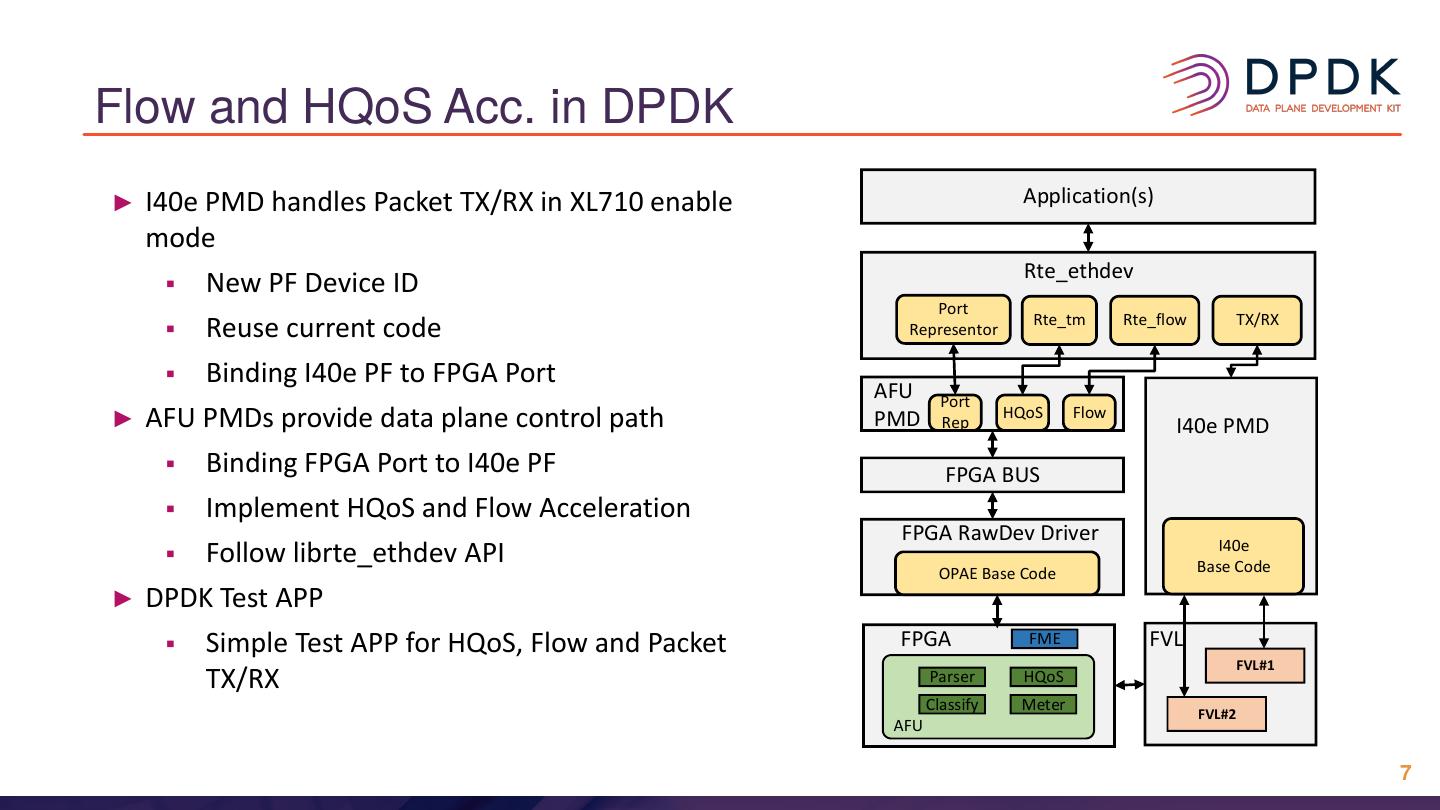

7 .Flow and HQoS Acc. in DPDK ► I40e PMD handles Packet TX/RX in XL710 enable Application(s) mode Rte_ethdev New PF Device ID Port Rte_tm Rte_flow TX/RX Reuse current code Representor Binding I40e PF to FPGA Port AFU Port ► AFU PMDs provide data plane control path PMD Rep HQoS Flow I40e PMD Binding FPGA Port to I40e PF FPGA BUS Implement HQoS and Flow Acceleration FPGA RawDev Driver I40e Follow librte_ethdev API Base Code OPAE Base Code ► DPDK Test APP Simple Test APP for HQoS, Flow and Packet FPGA FME FVL FVL#1 TX/RX Parser HQoS Classify Meter FVL#2 AFU 7

8 .Future work ► Enable more workload vBNG/vBRAS 5G FlexRan vRouter ► PAC N3000 Power Management 8

9 .Thanks