- 快召唤伙伴们来围观吧

- 微博 QQ QQ空间 贴吧

- 文档嵌入链接

- 复制

- 微信扫一扫分享

- 已成功复制到剪贴板

内存层次结构

展开查看详情

1 . ECE4680 Computer Organization and Architecture Memory Hierarchy ECE4680 Memory.1 2002-4-21 The Big Picture: Where are We Now? °The Five Classic Components of a Computer Processor Input Control Memory Datapath Output °Today’s Topic: Memory System ECE4680 Memory.2 2002-4-21

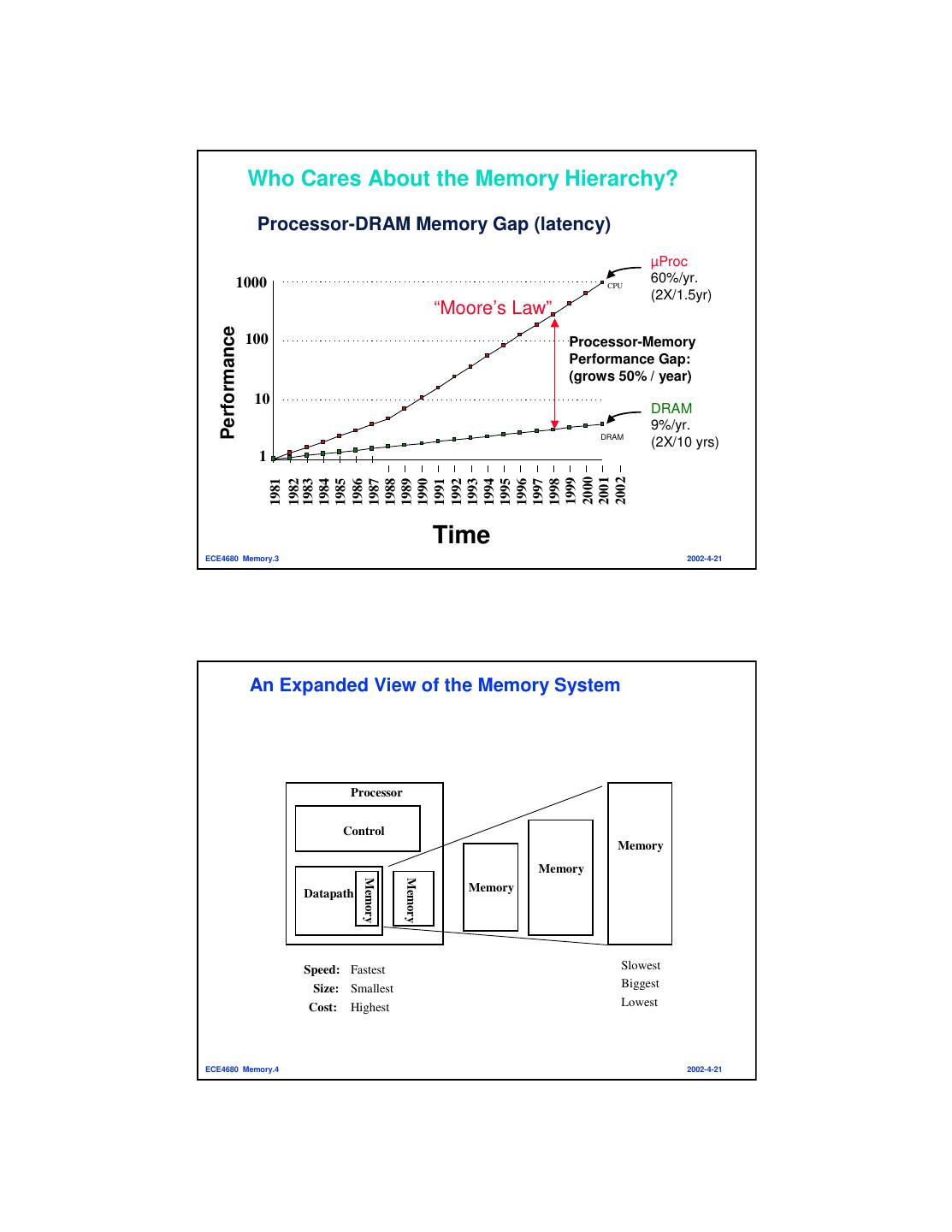

2 . Who Cares About the Memory Hierarchy? Processor-DRAM Memory Gap (latency) µProc 1000 CPU 60%/yr. (2X/1.5yr) “Moore’s Law” Performance 100 Processor-Memory Performance Gap: (grows 50% / year) 10 DRAM 9%/yr. DRAM (2X/10 yrs) 1 2000 2001 2002 1999 1984 1986 1988 1990 1993 1995 1997 1981 1982 1983 1985 1987 1989 1991 1992 1994 1996 1998 Time ECE4680 Memory.3 2002-4-21 An Expanded View of the Memory System Processor Control Memory Memory Memory Memory Datapath Memory Speed: Fastest Slowest Size: Smallest Biggest Cost: Highest Lowest ECE4680 Memory.4 2002-4-21

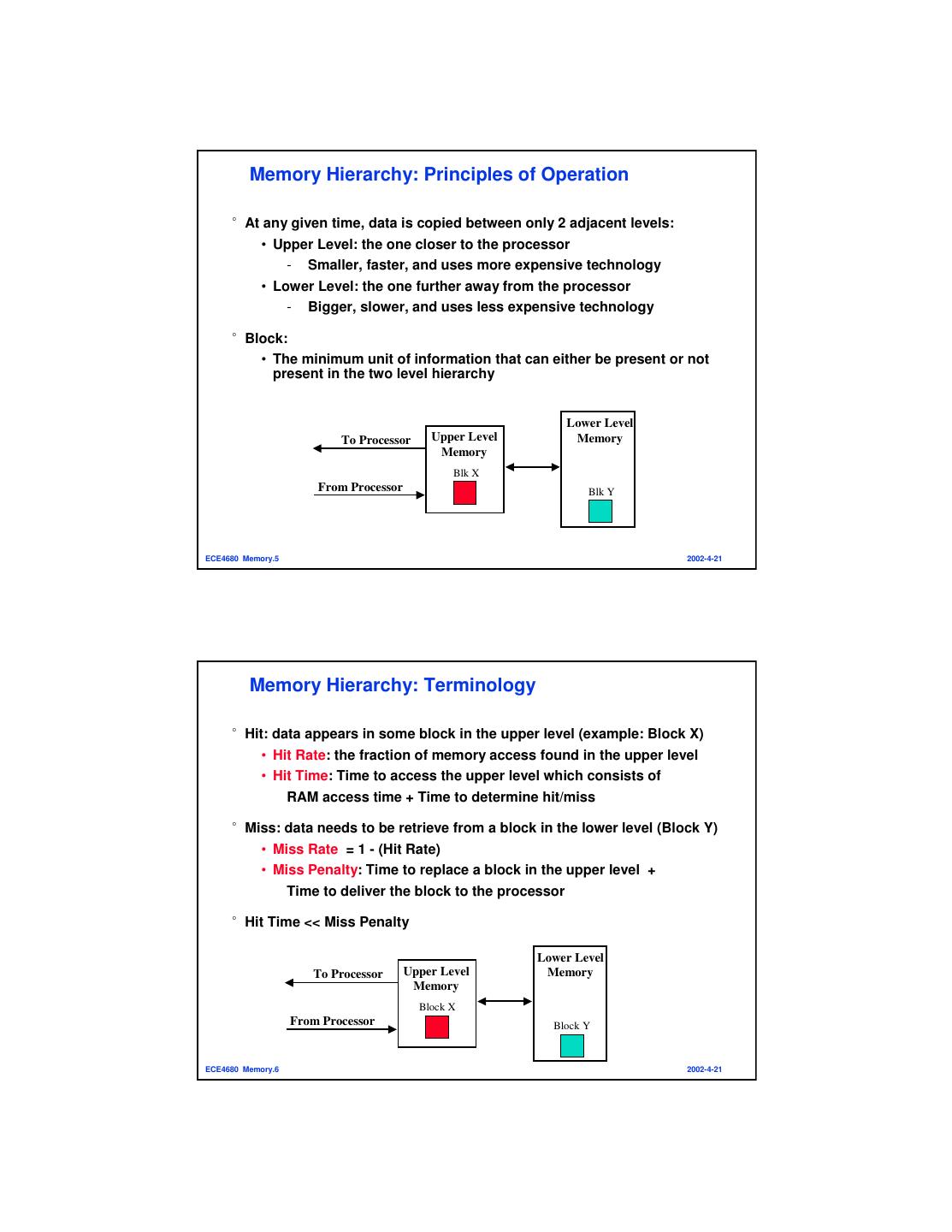

3 . Memory Hierarchy: Principles of Operation °At any given time, data is copied between only 2 adjacent levels: • Upper Level: the one closer to the processor - Smaller, faster, and uses more expensive technology • Lower Level: the one further away from the processor - Bigger, slower, and uses less expensive technology °Block: • The minimum unit of information that can either be present or not present in the two level hierarchy Lower Level To Processor Upper Level Memory Memory Blk X From Processor Blk Y ECE4680 Memory.5 2002-4-21 Memory Hierarchy: Terminology °Hit: data appears in some block in the upper level (example: Block X) • Hit Rate: the fraction of memory access found in the upper level • Hit Time: Time to access the upper level which consists of RAM access time + Time to determine hit/miss °Miss: data needs to be retrieve from a block in the lower level (Block Y) • Miss Rate = 1 - (Hit Rate) • Miss Penalty: Time to replace a block in the upper level + Time to deliver the block to the processor °Hit Time << Miss Penalty Lower Level To Processor Upper Level Memory Memory Block X From Processor Block Y ECE4680 Memory.6 2002-4-21

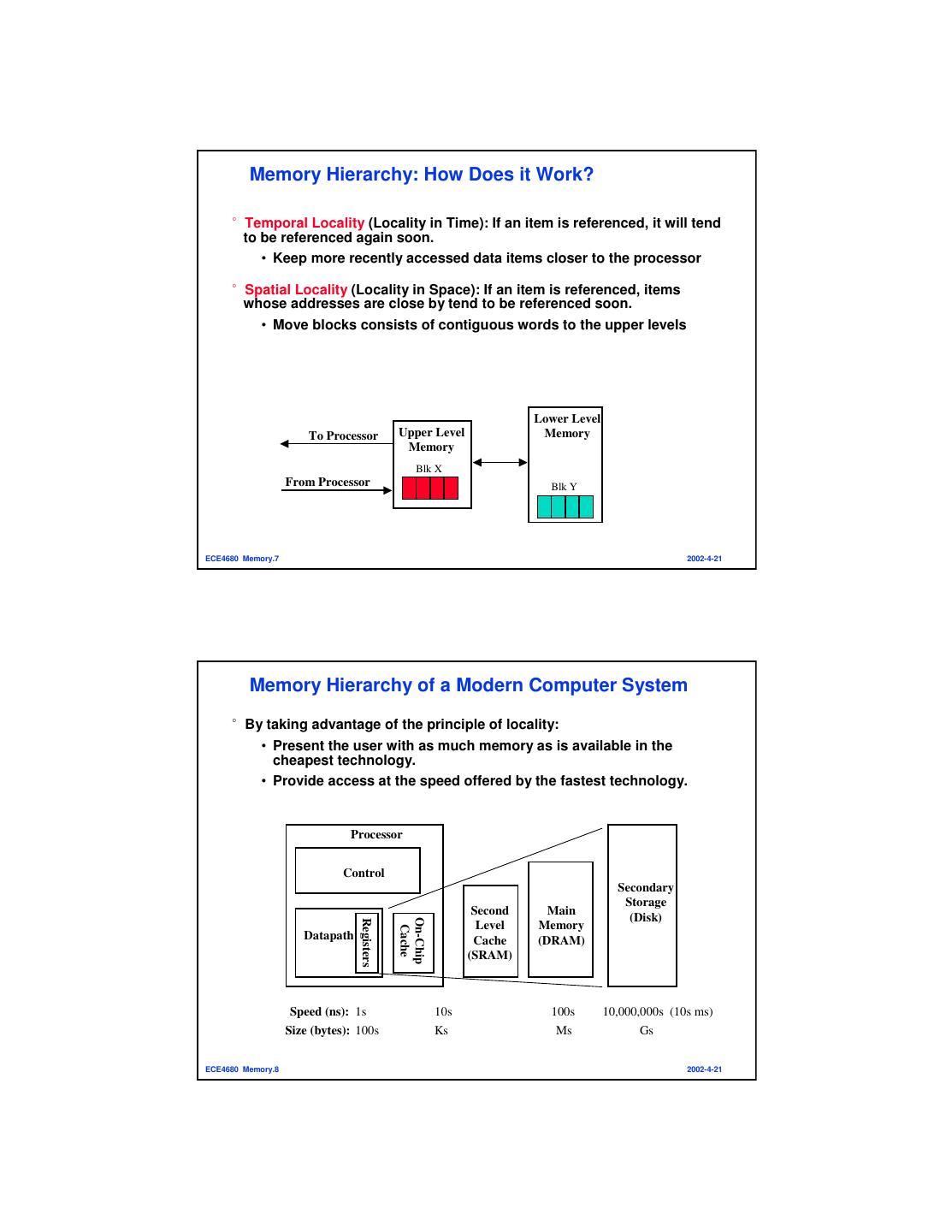

4 . Memory Hierarchy: How Does it Work? °Temporal Locality (Locality in Time): If an item is referenced, it will tend to be referenced again soon. • Keep more recently accessed data items closer to the processor °Spatial Locality (Locality in Space): If an item is referenced, items whose addresses are close by tend to be referenced soon. • Move blocks consists of contiguous words to the upper levels Lower Level To Processor Upper Level Memory Memory Blk X From Processor Blk Y ECE4680 Memory.7 2002-4-21 Memory Hierarchy of a Modern Computer System °By taking advantage of the principle of locality: • Present the user with as much memory as is available in the cheapest technology. • Provide access at the speed offered by the fastest technology. Processor Control Secondary Storage Second Main (Disk) On-Chip Registers Level Memory Cache Datapath Cache (DRAM) (SRAM) Speed (ns): 1s 10s 100s 10,000,000s (10s ms) Size (bytes): 100s Ks Ms Gs ECE4680 Memory.8 2002-4-21

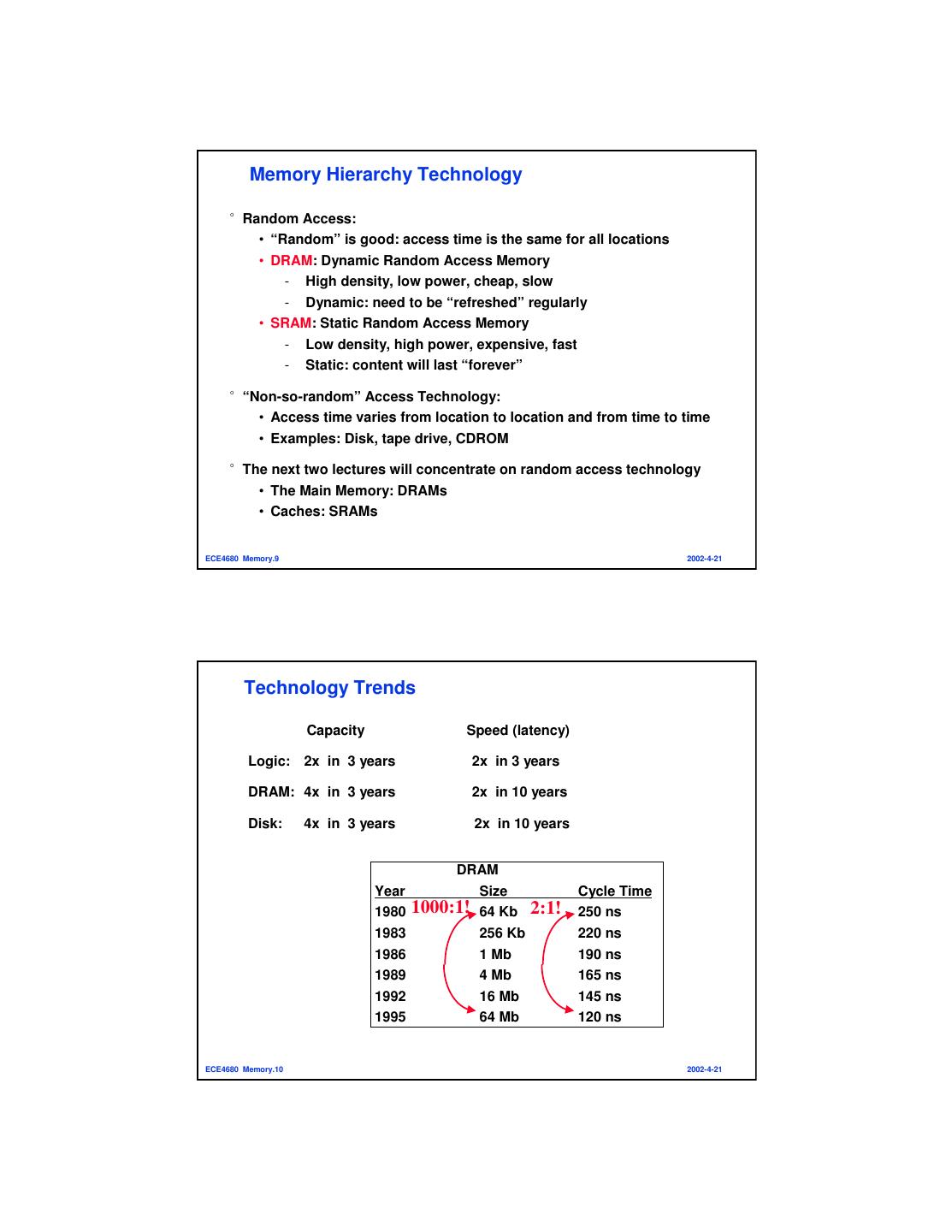

5 . Memory Hierarchy Technology °Random Access: • “Random” is good: access time is the same for all locations • DRAM: Dynamic Random Access Memory - High density, low power, cheap, slow - Dynamic: need to be “refreshed” regularly • SRAM: Static Random Access Memory - Low density, high power, expensive, fast - Static: content will last “forever” °“Non-so-random” Access Technology: • Access time varies from location to location and from time to time • Examples: Disk, tape drive, CDROM °The next two lectures will concentrate on random access technology • The Main Memory: DRAMs • Caches: SRAMs ECE4680 Memory.9 2002-4-21 Technology Trends Capacity Speed (latency) Logic: 2x in 3 years 2x in 3 years DRAM: 4x in 3 years 2x in 10 years Disk: 4x in 3 years 2x in 10 years DRAM Year Size Cycle Time 1980 1000:1! 64 Kb 2:1! 250 ns 1983 256 Kb 220 ns 1986 1 Mb 190 ns 1989 4 Mb 165 ns 1992 16 Mb 145 ns 1995 64 Mb 120 ns ECE4680 Memory.10 2002-4-21

6 . SPARCstation 20’s Memory System Overview Memory Controller Memory Bus (SIMM Bus) 128-bit wide datapath Memory Module 5 Memory Module 4 Memory Module 7 Memory Module 3 Memory Module 1 Memory Module 6 Memory Module 2 Memory Module 0 Processor Bus (Mbus) 64-bit wide Processor Module (Mbus Module) SuperSPARC Processor Instruction External Cache Cache Register File Data Cache ECE4680 Memory.11 2002-4-21 SPARCstation 20’s Memory Module °Supports a wide range of sizes: • Smallest: 4 MB = 16 2Mb DRAM chips, 8 KB of Page Mode SRAM • Biggest: 64 MB = 32 16Mb chips, 16 KB of Page Mode SRAM DRAM Chip 15 512 cols 256K x 8 = 2 MB DRAM Chip 0 One page 512 rows 256K x 8 512 × 8 SRAM = 2 Mb 8 bits bits<127:0> 512 × 8 SRAM bits<7:0> Memory Bus<127:0> ECE4680 Memory.12 2002-4-21

7 . Summary: °Two Different Types of Locality: • Temporal Locality (Locality in Time): If an item is referenced, it will tend to be referenced again soon. • Spatial Locality (Locality in Space): If an item is referenced, items whose addresses are close by tend to be referenced soon. °By taking advantage of the principle of locality: • Present the user with as much memory as is available in the cheapest technology. • Provide access at the speed offered by the fastest technology. °DRAM is slow but cheap and dense: • Good choice for presenting the user with a BIG memory system °SRAM is fast but expensive and not very dense: • Good choice for providing the user FAST access time. ECE4680 Memory.13 2002-4-21