- 快召唤伙伴们来围观吧

- 微博 QQ QQ空间 贴吧

- 文档嵌入链接

- 复制

- 微信扫一扫分享

- 已成功复制到剪贴板

计算机体系结构的世界

展开查看详情

1 . ECE 4680 Computer Architecture and Organization Lecture 1: A Short Journey to the World of Computer Architecture Basic Ideas and Definition Major Components of Software/Hardware Computer Revolution ece4680 Lect1 Intro.1 February 6, 2002 What is "Computer Architecture" ° Co-ordination of levels of abstraction Application Operating Compiler System Instruction Set Architecture Instr. Set Proc. I/O system Digital Design Circuit Design ° Merits of Abstraction/Layers/Hierarchy ° Under a set of rapidly changing Forces : technology, applications, Programming Languages, operating systems, history ece4680 Lect1 Intro.2 February 6, 2002

2 . Technology Trend: Clock rate 1,000 υυ υ υυ υ υυ R10000 υ υυυ υ υ 100 υυυ υυ υυ Pentium100 υυυυ υ Clock rate (MHz) υ υ υ υ υ υυ υυυυυυυυυ υ υ υυ υυυυ υ υ i80386 υυ 10 i8086 υ υ i80286 υ υ i8080 1 υ υ υ i8008 i4004 0.1 1970 1980 1990 2000 1975 1985 1995 2005 • 30% per year ---> today’s PC is yesterday’s Supercomputer ece4680 Lect1 Intro.3 February 6, 2002 Technology Trends: Transistor Count Growth 100,000,000 υ 10,000,000 υ υυυ υ υ υ R10000 υυυ υ υ υ Pentium υυ υυυυυ υ 1,000,000 υυυυυυυυ υ υυ Transistors υ υ υ υ i80386 υ i80286 υ υ υ R3000 100,000 υ υ υ R2000 υ i8086 10,000 υ υ υ i8080 υ i8008 i4004 1,000 1970 1980 1990 2000 1975 1985 1995 2005 - 40% per year, order of magnitude more contribution in 2 decades - More and more functions can be performed by a CPU - Similar story for storage: capacity increased by 1000x over ten years, speed only 2x ece4680 Lect1 Intro.4 February 6, 2002

3 . Technology => dramatic change °Processor • logic capacity: about 30% per year • clock rate: about 20% per year °Memory • DRAM capacity: about 60% per year (4x every 3 years) • Memory speed: about 10% per year • Cost per bit: improves about 25% per year °Disk • capacity: about 60% per year ece4680 Lect1 Intro.5 February 6, 2002 Performance Trends 1000 Supercomputers 100 Mainframes Performance 10 Minicomputers Microprocessors 1 0.1 1965 1970 1975 1980 1985 1990 1995 2000 Year ece4680 Lect1 Intro.6 February 6, 2002

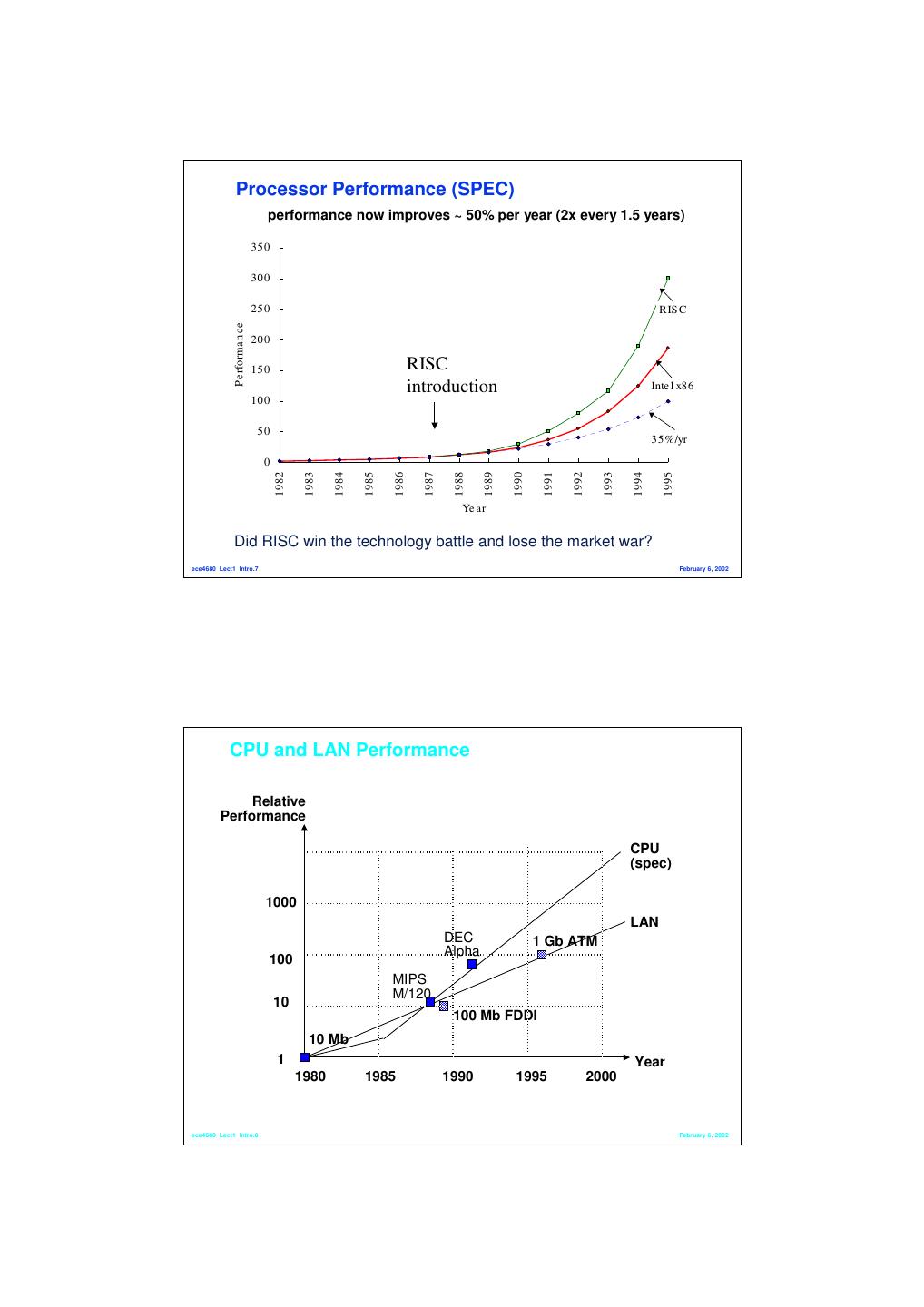

4 . Processor Performance (SPEC) performance now improves ~ 50% per year (2x every 1.5 years) 350 300 250 RIS C P e rforma nce 200 150 RISC introduction Inte l x86 100 50 35%/yr 0 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995 Ye ar Did RISC win the technology battle and lose the market war? ece4680 Lect1 Intro.7 February 6, 2002 CPU and LAN Performance Relative Performance CPU (spec) 1000 LAN DEC 1 Gb ATM Alpha 100 MIPS M/120 10 100 Mb FDDI 10 Mb 1 Year 1980 1985 1990 1995 2000 ece4680 Lect1 Intro.8 February 6, 2002

5 . Moore’s Law Moore’s Law (1965) The number of transistors on a microchip doubles about every 18-24 months, The speed of a microprocessor doubles about every 18-24 months, The price of a microchip drops about 48% every 18-24 months, assuming the performance metric (processor speed or memory capacity) of the chip stays the same. Official Definition of Moore’s Law : http://www.intel.com/intel/museum/25anniv/hof/moore.htm 6 ece4680 Lect1 Intro.9 February 6, 2002 H Notations and Conventions for Numbers P CPrefixAppendix1: Notations Abbreviation and ConventionsNumeric Meaning for Numbers Value −3 Amill m One thousandth 10 micro µ One millionth 10 −6 2 nano n One billionth 10 −9 0 0 pico p One trillionth 10 −12 1 femto f One quadrillionth 10 −15 atta a One quintillionth 10 −18 kilo K (or k) Thousand 10 3 or 210 mega M Million 10 6 or 2 20 giga G Billion 10 9 or 2 30 tera T Trillion 10 12 or 2 40 peta P Quadrillion 10 15 or 2 50 61 exa E Quintillion 10 18 or 2 60 Even the measure unit is changing !!! ece4680 Lect1 Intro.10 February 6, 2002

6 . How they predict the future °Popular Science , 1949 "Computers in the future may weight no more than 1.5 tons" °Thomas Watson, Chairman of IBM , 1943 "I think there is a world market for maybe five computers" °Ken Olsen, founder and president of Digital Equipment Corp, 1957 "There is no reason anyone would want a computer in their home" °Charles H. Duell, Commissioner, U.S. Office of patents "Everything that can be invented has been invented" °Bill Gates, 1981 "640K ought to be enough for anybody" ece4680 Lect1 Intro.11 February 6, 2002 Computer Arch. = Instruction Set Arch. + Organization Computer Design Instruction Set Design Computer Hardware Design ° Machine Language ° Machine Implementation ° Compiler View ° "Computer Architecture" ° Logic Designer's View ° "Instruction Set Processor" ° "Processor Architecture" "Building Architect" ° "Computer Organization" "Construction Engineer" ece4680 Lect1 Intro.12 February 6, 2002

7 . Instruction Set Architecture . . . the attributes of a [computing] system as seen by the programmer, i.e. the conceptual structure and functional behavior, as distinct from the organization of the data flows and controls the logic design, and the physical implementation. Amdahl, Blaw, and Brooks, 1964 SOFTWARE -- Organization of Programmable Storage -- Data Types & Data Structures: Encodings & Representations -- Instruction Formats -- Instruction (or Operation Code) Set -- Modes of Addressing and Accessing Data Items and Instructions -- Exceptional Conditions ece4680 Lect1 Intro.13 February 6, 2002 MIPS R3000 Instruction Set Architecture ° Instruction Categories • Load/Store • Computational R0 - R31 • Jump and Branch • Floating Point - coprocessor • Memory Management PC • Special HI LO Instruction Format OP rs rt rd sa funct OP rs rt immediate OP target ece4680 Lect1 Intro.14 February 6, 2002

8 . Organization ISA Level FUs & Interconnect Logic Designer's View -- Capabilities & Performance Characteristics of Principal Functional Units (e.g., Registers, ALU, Shifters, Logic Units, etc. -- Ways in which these components are interconnected -- nature of information flows between components -- logic and means by which such information flow is controlled. Choreography of FUs to realize the ISA Register Transfer Level Description ece4680 Lect1 Intro.15 February 6, 2002 Example Organization °TI SuperSPARCtm TMS390Z50 in Sun SPARCstation20 MBus Module SuperSPARC Floating-point Unit L2 CC DRAM Integer Unit $ MBus Controller Inst Ref Data L64852 MBus control M-S Adapter STDIO Cache MMU Cache SBus serial Store SCSI kbd SBus mouse Buffer DMA Ethernet audio RTC Bus Interface SBus Boot PROM Cards Floppy ece4680 Lect1 Intro.16 February 6, 2002

9 . Measurement and Evaluation Architecture is an iterative process Design -- searching the space of possible designs -- at all levels of computer systems Analysis Creativity Cost / Performance Analysis Good Ideas Mediocre Ideas Bad Ideas ece4680 Lect1 Intro.17 February 6, 2002 Levels of Representation temp = v[k]; High Level Language v[k] = v[k+1]; Program v[k+1] = temp; Compiler lw $15, 0($2) Assembly Language Program lw $16, 4($2) Assembler sw $16, 0($2) sw $15, 4($2) Machine Language Program Machine Interpretation Control Signal Spec ece4680 Lect1 Intro.18 February 6, 2002

10 . ECE468: Course Overview Computer Design Instruction Set Deign Computer Hardware Design ° Machine Language ° Machine Implementation\ ° Compiler View ° Logic Designer's View ° "Computer Architecture" ° "Processor Architecture" ° "Instruction Set Processor" ° "Computer Organization" "Building Architect" Construction Engineer Few people design computers! Very few design instruction sets! Many people design computer components. Very many people are concerned with computer function, in detail. ece4680 Lect1 Intro.19 February 6, 2002 ECE468:So what's in it for me? °In-depth understanding of the inner-workings of modern computers, their evolution, and trade-offs present at the hardware/software boundary. • Insight into fast/slow operations that are easy/hard to implementation hardware °Experience with the design process in the context of a large complex (hardware) design. • Functional Spec --> Control & Datapath °Learn how to completely design a correct single processor computer. • No magic required to design a computer °Foundation for students aspiring to work in computer architecture. °Others: solidifies an intuition about why hardware is as it is. ece4680 Lect1 Intro.20 February 6, 2002

11 . The SPARCstation 20 SPARCstation 20 Memory Memory SIMMs Controller Memory Bus MBus Disk MBu Slot 1 s SBus Slot 1 SBus Slot 3 Tape MBu Slot 0 s SBus Slot 0 SBus Slot 2 SBus SCSI MSBI Bus SEC MACIO Keyboard Floppy External Bus & Mouse Disk ece4680 Lect1 Intro.21 February 6, 2002 Levels of Organization SPARCstation 20 Computer SPARC Memory Devices Processor Control Input Datapath Output ece4680 Lect1 Intro.22 February 6, 2002

12 . The Underlying Network SPARCstation 20 Memory Memory Bus Controller Standard I/O Bus: Processor Bus: SCSI Bus MBus Sun’s High Speed I/O Bus: SBus MSBI SEC MACIO Low Speed I/O Bus: External Bus ece4680 Lect1 Intro.23 February 6, 2002 Processor and Caches SPARCstation 20 MBus Module SuperSPARC Processor MBus MBu Slot 1 Registers Datapath s MBu Slot 0 s Internal Control Cache External Cache ece4680 Lect1 Intro.24 February 6, 2002

13 . Memory SPARCstation 20 SIMM Slot 4 SIMM Slot 0 SIMM Slot 1 SIMM Slot 2 SIMM Slot 3 SIMM Slot 5 SIMM Slot 6 SIMM Slot 7 Memory Memory Bus Controller DRAM SIMM DRAM DRAM DRAM DRAM DRAM DRAM DRAM DRAM DRAM DRAM ece4680 Lect1 Intro.25 February 6, 2002 Input and Output (I/O) Devices SPARCstation 20 ° SCSI Bus: Standard I/O Devices ° SBus: High Speed I/O Devices ° External Bus: Low Speed I/O Device Disk SBus Slot 1 SBus Slot 3 Tape SBus Slot 0 SBus Slot 2 SBus SCSI Bus SEC MACIO Keyboard Floppy External Bus & Mouse Disk ece4680 Lect1 Intro.26 February 6, 2002

14 . Standard I/O Devices SPARCstation 20 ° SCSI = Small Computer Systems Interface ° A standard interface (IBM, Apple, HP, Sun ... etc.) Disk ° Computers and I/O devices communicate with each other Tape ° The hard disk is one I/O device resides on the SCSI Bus SCSI Bus ece4680 Lect1 Intro.27 February 6, 2002 High Speed I/O Devices SPARCstation 20 ° SBus is SUN’s own high speed I/O bus ° SS20 has four SBus slots where we can plug in I/O devices ° Example: graphics accelerator, video adaptor, ... etc. ° High speed and low speed are relative terms SBus Slot 1 SBus Slot 3 SBus Slot 0 SBus Slot 2 SBus ece4680 Lect1 Intro.28 February 6, 2002

15 . Slow Speed I/O Devices SPARCstation 20 ° The are only four SBus slots in SS20--”seats” are expensive ° The speed of some I/O devices is limited by human reaction time--very very slow by computer standard ° Examples: Keyboard and mouse ° No reason to use up one of the expensive SBus slot Keyboard Floppy External Bus & Mouse Disk ece4680 Lect1 Intro.29 February 6, 2002 Summary °ISA--Principle of abstraction • Hiding details from the level above • Both software designers and hardware designers comply with °All computers consist of five components • Processor: (1) datapath and (2) control • (3) Memory • (4) Input devices and (5) Output devices °Not all “memory” are created equally • Cache: fast (expensive) memory are placed closer to the processor • Main memory: less expensive memory--we can have more °Input and output (I/O) devices has the messiest organization • Wide range of speed: graphics vs. keyboard • Wide range of requirements: speed, standard, cost ... etc. • Least amount of research (so far) ece4680 Lect1 Intro.30 February 6, 2002