- 快召唤伙伴们来围观吧

- 微博 QQ QQ空间 贴吧

- 文档嵌入链接

- 复制

- 微信扫一扫分享

- 已成功复制到剪贴板

FPGA and Virtualization Technology in DPDK to Accelerating

展开查看详情

1 .Zhang Tianfei Rosen Xu

2 .Agenda Part 1: FPGA and OPAE - Intel® FPGAs and the Modern Datacenter - Platform Options and the Acceleration Stack - FPGA Hardware overview - Open Programmable Acceleration Engine (OPAE) Part 2: FPGA, OPAE and DPDK - DPDK Overview - FPGA in cloud Networking - FPGA Acceleration on DPDK - DPDK for vSwitch FPGA Acceleration 2

3 .Part 1: FPGA and OPAE 3

4 . Data Movement and Processing Explosion Markets Government Enterprise Cloud >20B Communications Connected Devices 5G Wireless by 2020‡ Infrastructure Network Storage Compute Hyper-connected World Workloads Security Big Data Processing and Analytics Video processing and transcode Big Data Processing Artificial Intelligence & Machine Learning and Analytics High-Performance Packet processing Computing Demands ‡ Source: “Gartner Says 8.4 Billion Connected ‘Things’ Will Be in Use in 2017, Up 31 Percent From Network 2016”, 2/7/2017, http://www.gartner.com/newsroom/id/3598917 (Table 1 - IoT Units Platforms Group 4 Installed Base by Category, 2020 column – Grand Total, including consumer+business units)

5 .Acceleration Assist To Propel DatA Insight & Operational Efficiency Workload N Workload Optimization: Workload 2 Ensure Intel® Xeon® CPU cores Workload 1 serve highest value processing Efficient Performance: Improve performance/watt Real-Time: High bandwidth connectivity and z low-latency parallel processing Milliseconds Developer Advantage: Code re-use across Intel FPGA data center products The Intel® Xeon® processor with FPGA acceleration can reduce TCO and solve new problems Network Platforms Group 5

6 . Intel® FPGA Data Center Form FactorS Options Enabled By The Acceleration Stack for Intel® Xeon® CPU with FPGAs PCIe Acceleration Cards Server Platform Option with In-Package FPGA System flexibility with Intel Xeon CPU SKU options Coherent interface benefits software developers Dedicated local memory Superior performance for bandwidth & latency sensitive applications Can be slotted into 1U servers Choose the Intel FPGA form factor matched to your application needs 1UPI = Intel® Ultra Path Interconnect 2HSSI Network Platforms Group = High Speed Serial Interface 6

7 .The Intel® Application Developer Advantage Acceleration Stack for Intel® Xeon® CPU with FPGAs Intel Environment Code re-use IP Libraries Acceleration Stack for Intel® Xeon® CPU with FPGAs – Enhanced Performance, Simplified • Saves developer time to focus on unique value-add of their solution • Enables unprecedented code re-use across multiple Intel FPGA form-factor products • World’s first common developer interface for Intel FPGA data center products • Optimized and simplified hardware and software APIs provided by Intel • Enables easier development and deployment of Intel FPGAs for workload optimization The stable and optimized foundation for building your Intel FPGA-accelerated solution Network Platforms Group 7

8 . Acceleration Stack for Intel® Xeon® CPU with FPGAs Enhanced Performance, Simplified Dynamically Allocate Intel® FPGAs for Workload Optimization Rack-Level Solutions Rack Scale Design Simplified Application Development User Applications Deep Learning, Networking, Genomics, etc. Leverage Common Frameworks Industry Standard SW Frameworks Fast-Track Your Performance Acceleration Libraries LZ4, Snappy, etc. Workload Optimization with Less Effort Intel Developer Tools (Intel Parallel Studio XE, Intel FPGA SDK for OpenCL™, Intel Quartus® Prime) Common Developer Interface for Intel Acceleration Environment FPGA Data Center Products (Intel Acceleration Engine with OPAE Technology, FPGA Interface Manager (FIM)) Intel Hardware Intel® delivers a system-optimized solution stack for your data center workloads OpenCL and the OpenCL logo are trademarks of Apple Inc. used by permission by Khronos Network Platforms Group 8 Logos and names provided for illustrative purposes only. Current availability may be different.

9 . Open Programmable Acceleration Engine (OPAE) Technology Simplified FPGA Programming Layer for Application Developers Consistent cross-platform API Minimal software overhead and latency Supports virtual machines and bare metal platforms Open source code licensing and developer community • Intel FPGA drivers being upstreaming to Linux kernel • Intel FPGA userspace drivers have merged into DPDK Start developing for Intel FPGAs with OPAE today: http://01.org/OPAE **ASE requires Acceleration Functions written in RTL and a properly installed RTL simulator: Supports: Red Hat Enterprise Linux* 7.3 w/ kernel 4.7, Network Platforms Group 9 Synopsys* VCS-MX, Mentor Graphics* ModelSim-SE*/QuestaSim Intel® Xeon® Processors v4 or newer

10 . Acceleration Environment Common Developer Interface For Intel FPGA Data Center Products CPU FPGA Accelerator Function User Application (Developer created or & Libraries provided by Intel) Accelerator Function Interfaces Optimized and simplified Intel® Acceleration Engine with hardware and software FPGA Interface Manager (FIM) OPAE1 Technology APIs provided by Intel OPAE Hypervisor & OS FPGA CPU HSSI3 UPI2/PCIe* 1OPAE = Open Programmable Acceleration Engine Supports: Red Hat Enterprise Linux* 7.3 w/ kernel 4.7, 2UPI Network = Intel® Platforms Ultra PathGroup Interconnect 10 3HSSI Intel® Xeon® Processors v4 or newer = High Speed Serial Interface

11 .FPGA Interface Manager (FIM) overview Device memory organized in Device Feature List data structure Supported features exposed through Device Feature List 11

12 .FPGA Interface Manager (FIM) Details FPGA Management Engine – Provides: power and thermal management, error reporting, partial reconfiguration, performance reporting, and other infrastructure functions. – Each FPGA has one FME, accessible through the physical function. Port – Interface between the static FPGA fabric (FIM) and a partially reconfigurable region containing an Accelerated Function Unit (Accelerator Function). – Controls communication from SW and exposes features such as reset and debug. Accelerated Function Unit – Attached to a port and exposes a MMIO region for accelerator-specific control registers. 12

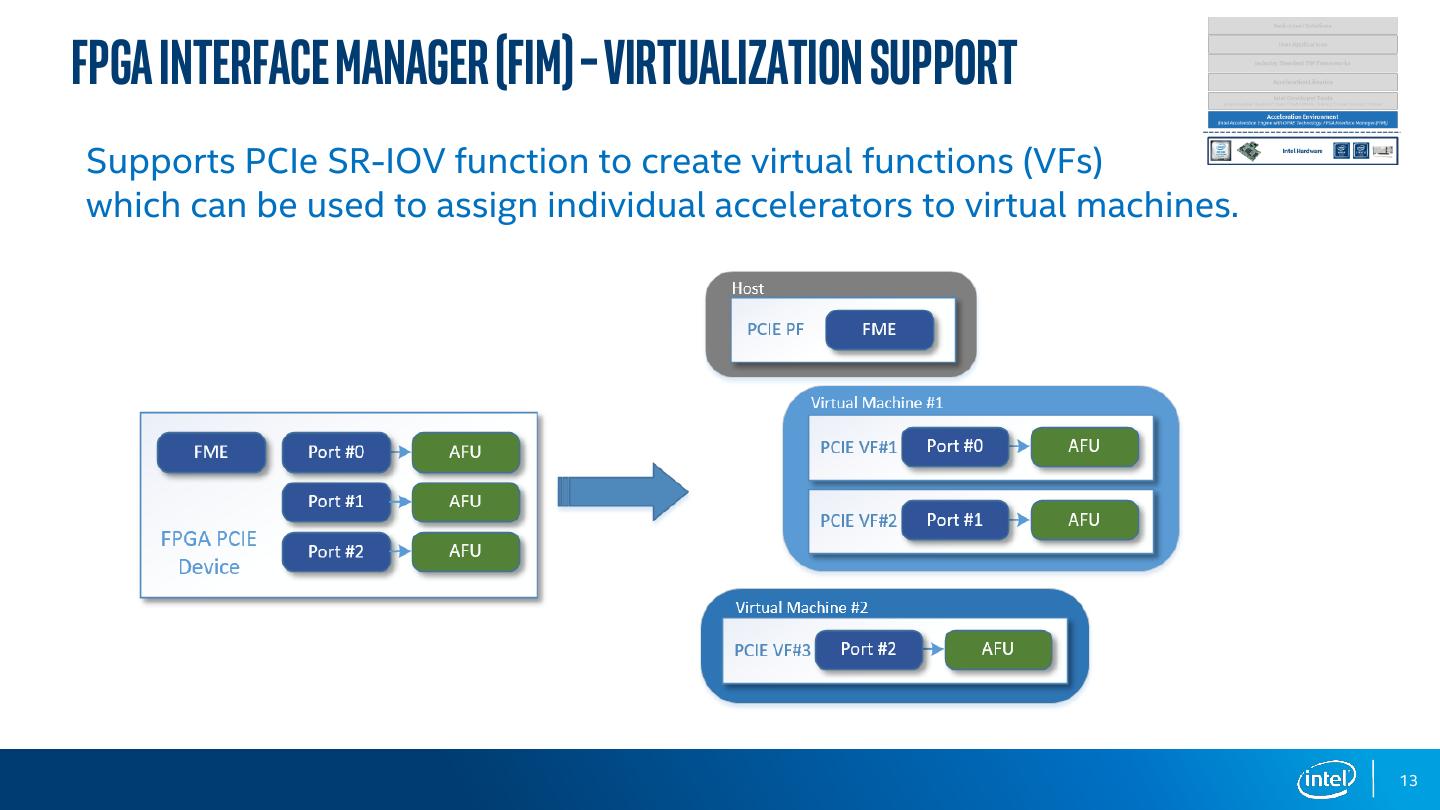

13 .FPGA Interface Manager (FIM) – Virtualization Support Supports PCIe SR-IOV function to create virtual functions (VFs) which can be used to assign individual accelerators to virtual machines. 13

14 .OPAE USERSPACE DRIVER infrastructure DPDK Application Non-DKDK Application DPDK Framework standalone Framework OPAE hardware layer API ifpga base Map Card other FPGA code base code 14

15 .OPAE User space Driver Architecture (Bare metal case) PF on Host VF0 on VM0 VFn on VMn Application DPDK Device NON-DPDK PMD User-Space Driver FPGA access FPGA management networking access Customer App OPAE libopae-c DPDK PMD OPAE API API user space kernel space PF/VF management FPGA FME driver FPGA AFU driver VFIO FPGA kernel PCIe driver ► FPGA Management by OPAE Kernel Driver (Upstream in progress) ► DPDK in VM with Normal PMD 15

16 . Summary OPAE is powerful and open software stack for FPGA to accelerating applications. OPAE can offer two kinds of drivers: user space driver solution: has merged into DPDK 18.05 kernel driver solution: upstreaming now Start developing for Intel FPGAs with OPAE today: http://01.org/OPAE 16

17 .Part 2: FPGA, OPAE and DPDK 17

18 .DPDK Framework – BIG Picture ? Event DPI ? Handler RegEx User stack IPsec VNF Data Plane APIs Run time Crypto Classifier Compression Virtualizatio Physical Container n * Other names and brands may be claimed as the property of others. 18

19 .FPGA in cloud Networking Opportunities – Enhancing Performance: Provide NIC ASIC liked performance – Changing dynamically: Flexible enough for adding new feature Problems – Longer design cycle than software: Compilation, Analysis & Synthesis, Fitter(Place & Router), Assembler, Timing – Online upgrade affecting business: PCIe rescan and driver reprobe * Other names and brands may be claimed as the property of others. 19

20 .Partial Reconfiguration (PR) With Partial Reconfigure(PR) parts of Bit Stream, FPGA not only provides one kinds of accelerator but also provides many types of accelerators at the same time – Hot upgraded – Resources time-shared – Fault tolerance How DPDK fully support FPGA? – Which type of DPDK Device can provide FPGA PR? – How can we bind DPDK Driver to FPGA Partial Bit Stream? * Other names and brands may be claimed as the property of others. 20

21 . FPGA Acceleration on DPDK - Scope rte_bus_list pci_device_list pci_driver_list constructor mcp_ Ixgb I40e mcp_ ifpga pci ixgb i40e fpga 1 _drv _drv drv rte_bus_register raw_dev_array afu_list INSERT to rte_bus_list afu_ afu_ dev_ crypto eth rawdev.ops fpga …… ENUMERATE & PR 2 INSERT AFU Device rte_ifpga_driver_ afu_driver_list register drv_ drv_ rte_eal_hotplug_ INSERT to afu_driver_list crypto eth add PROBE AFU Driver Rawdev probed as PCI Driver takes FPGA Configuration(Download/PR) 2 scans: FPGA PCI Device Scan(1st Scan) and AFU Scan(2nd Scan) OPAE Provides Common lib and API for low level FPGA management & accelerator access * Other names and brands may be claimed as the property of others. 21

22 .FPGA Acceleration on DPDK - Architecture DPDK Application Bare metal Application DPDK Device PMD Custom User space driver crypto FPGA Mgmt Network Path (partial reconfiguration) (NIC) FPGA Accelerator event librte_rawdev librte_ethdev OPAE High Level APIs fpga bus Eth driver (AFU) DPDK PCI Bus DPDK FPGA Device Driver OPAE Hardware Layer API Intel fpga base code User Space Kernel Space VFIO * Other names and brands may be claimed as the property of others. 22

23 .DPDK for vSwitch FPGA Acceleration OVSDB vswitchd SW Data path INIT system Flow SETUP port_ ethdev rte_flow rte_tm rte_mtr representors AFU Flow+ metering/ switch port HQoS PMD actions policying representation FPGA BUS vSwitch AFU FPGA Rawdev Driver OPAE FPGA Rate I/O I/O Classify FIB and Action Meter HQoS DMA Limit * Other names and brands may be claimed as the property of others. 23

24 . Summary FPGA BUS is in DPDK 18.05 Start developing for DPDK with OPAE : http://dpdk.org/doc/guides/rawdevs/ifpga_rawdev.html 24

25 .