- 快召唤伙伴们来围观吧

- 微博 QQ QQ空间 贴吧

- 文档嵌入链接

- 复制

- 微信扫一扫分享

- 已成功复制到剪贴板

调用指令

展开查看详情

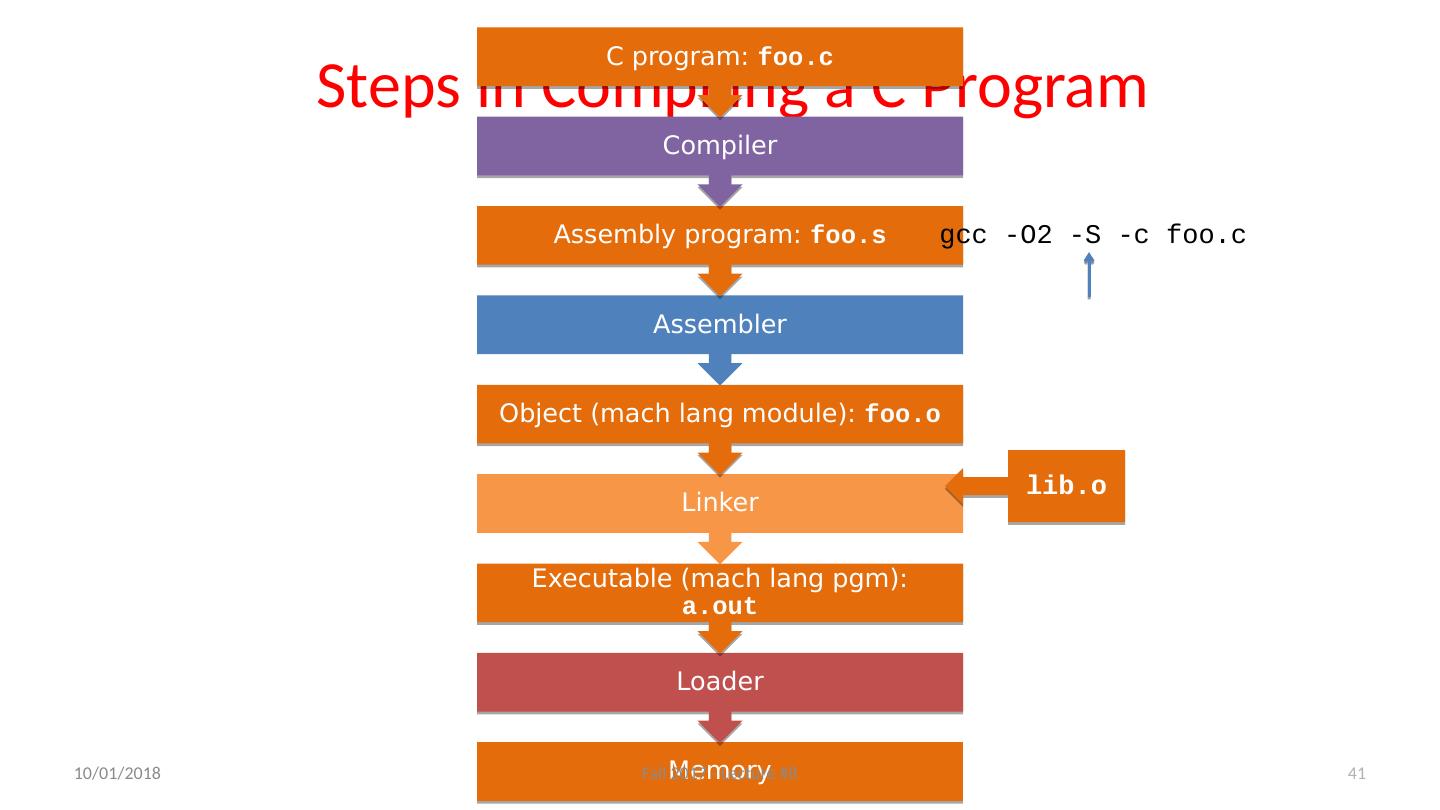

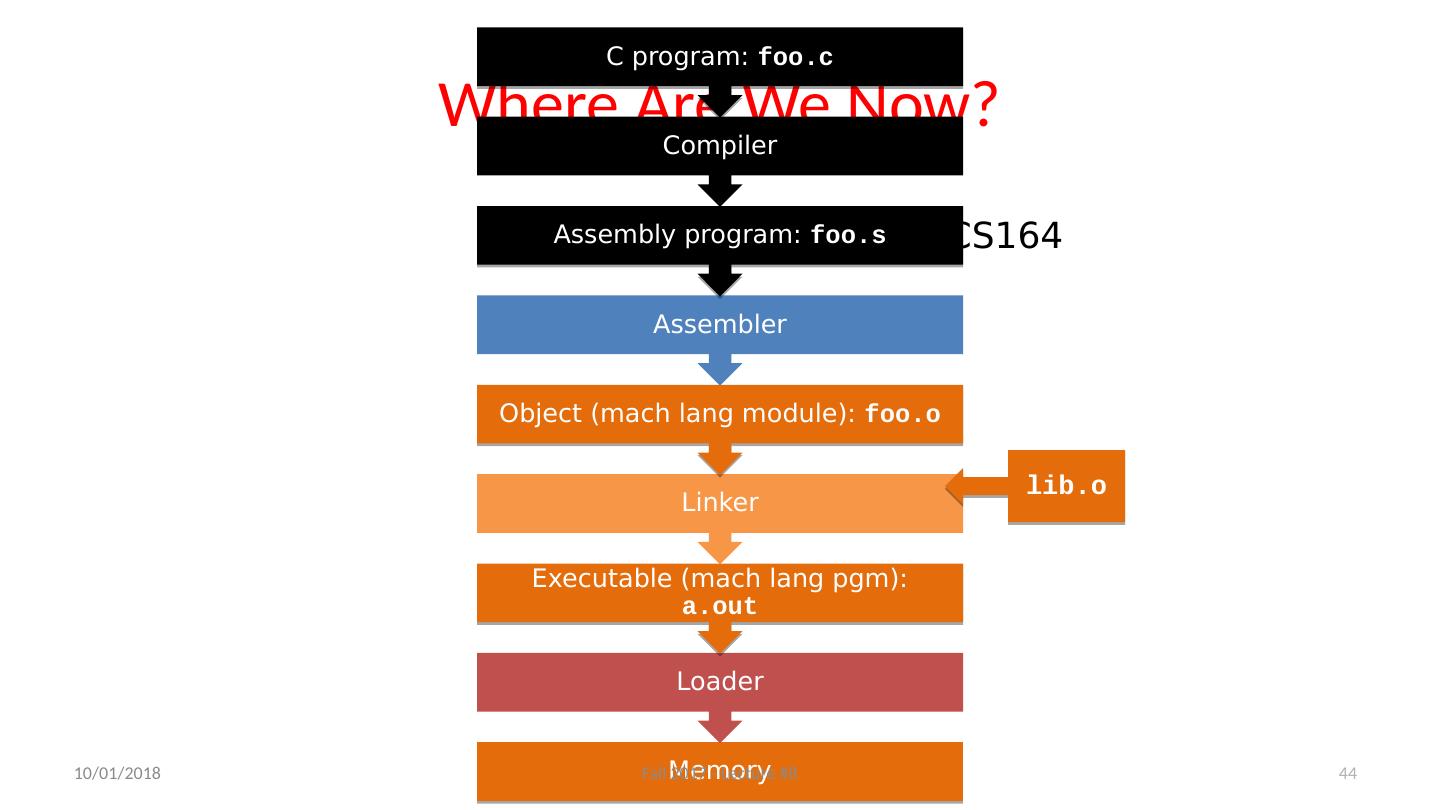

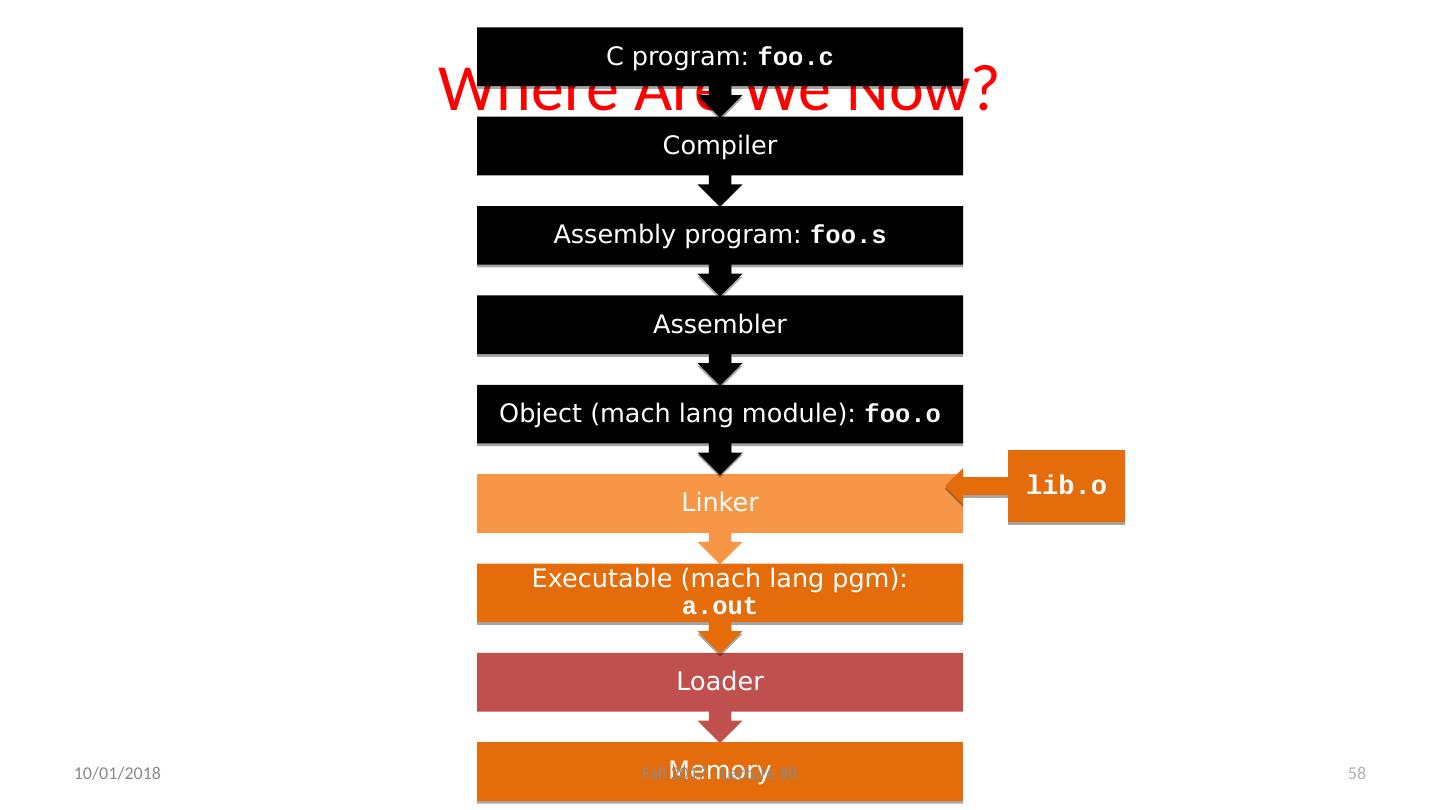

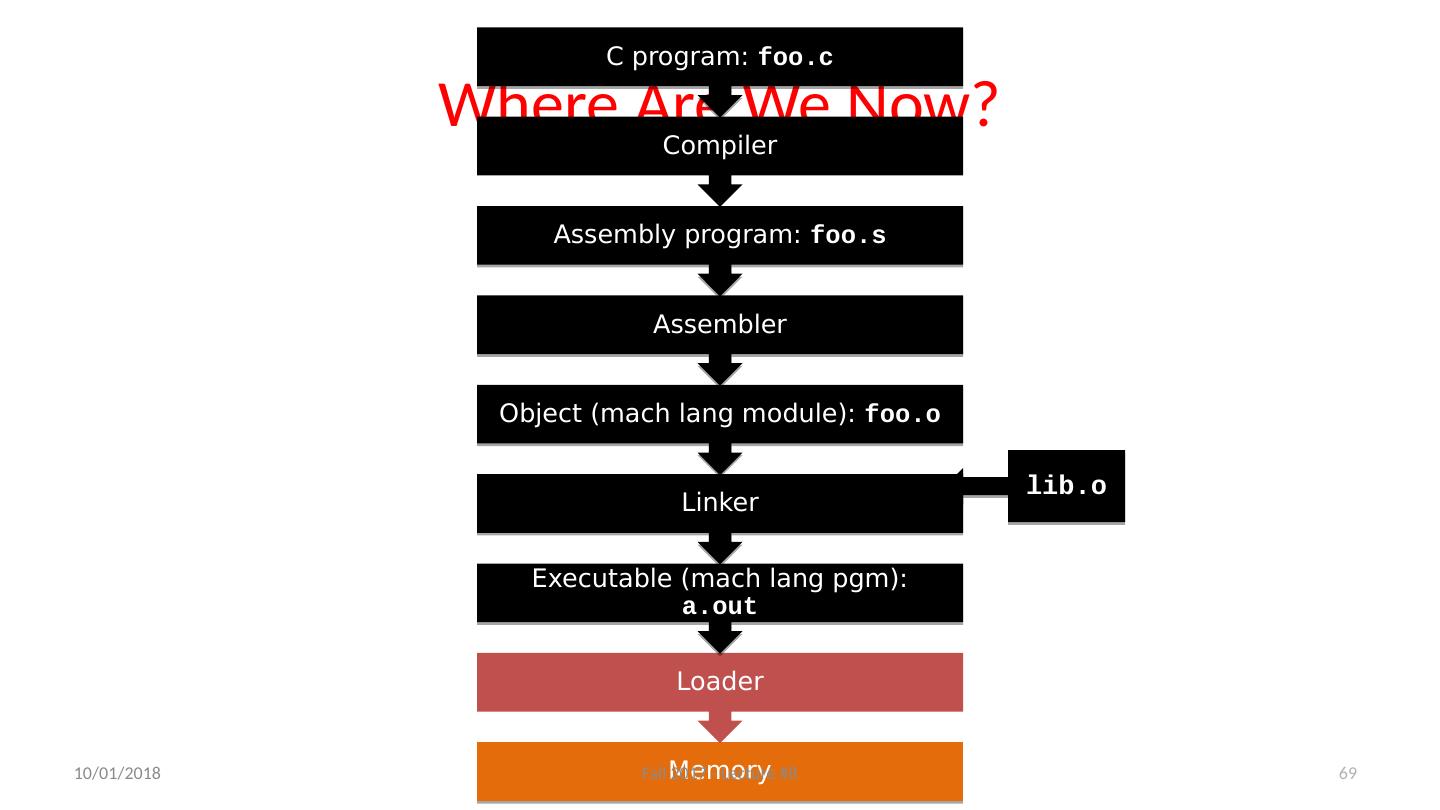

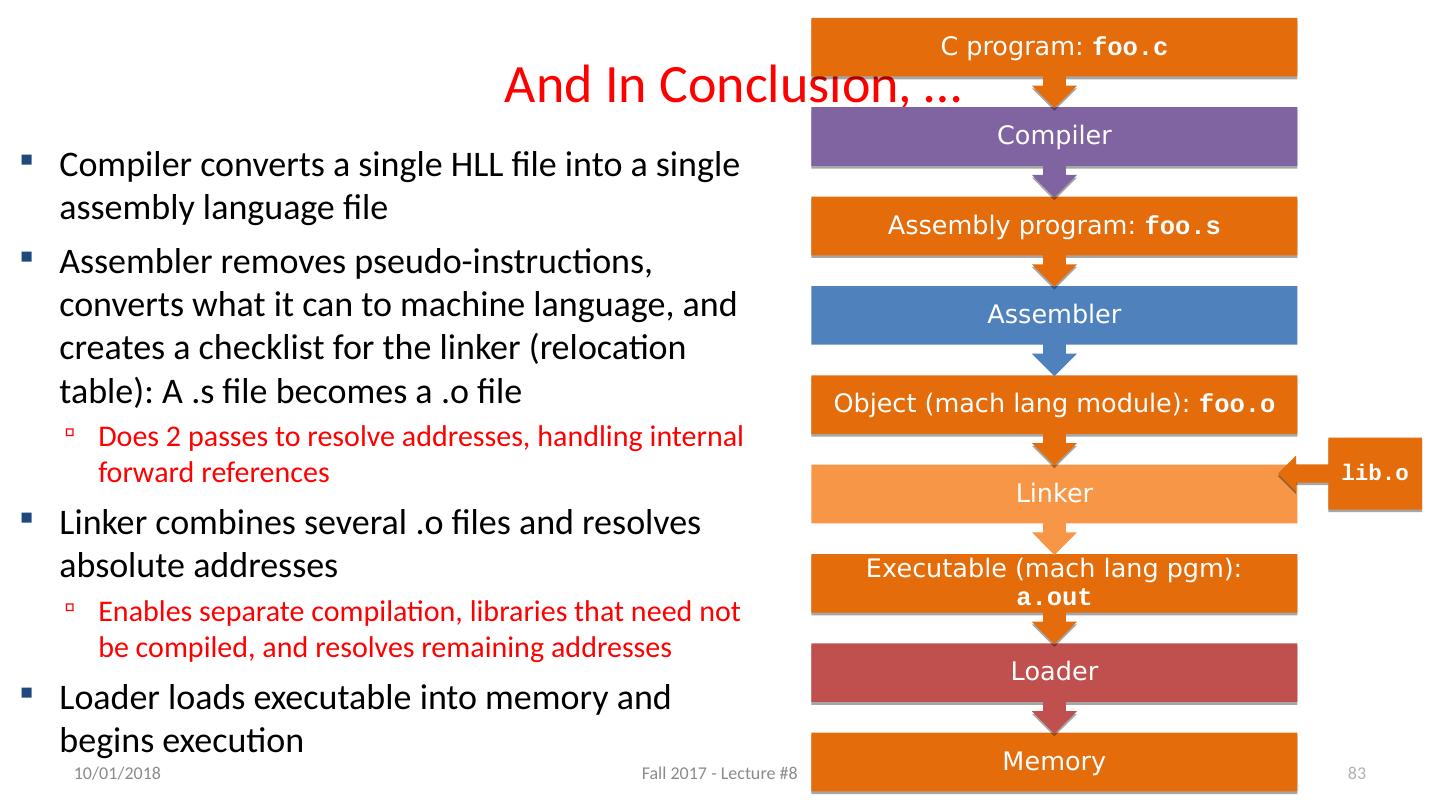

1 .CS 61C: Great Ideas in Computer Architecture Running a Program - CALL (Compiling , Assembling, Linking, and Loading) Instructors: Krste Asanović & Randy H. Katz http://inst.eecs.Berkeley.edu/~cs61c/fa17 9/19/17 Fall 2017 - Lecture #8 1

2 .Outline Review Instruction Formats + J/JAL Multiply and Divide Interpretation vs. Translation Assembler Linker Loader And in Conclusion … 9/19/17 Fall 2017 - Lecture #8 2

3 .Outline Review Instruction Formats + J/JAL Multiply and Divide Interpretation vs. Translation Assembler Linker Loader And in Conclusion … 9/19/17 Fall 2017 - Lecture #8 3

4 .Review: Components of a Computer 4 Fall 2017 - Lecture #8 9/19/17 Processor Control Datapath PC Registers Arithmetic & Logic Unit (ALU) Memory Input Output Bytes Enable? Read/Write Address Write Data Read Data Processor-Memory Interface I/O-Memory Interfaces Program Data Instructions

5 .Review: RISC-V Instruction Formats 5 Fall 2017 - Lecture #8 9/19/17 r d = rs1 OP rs2 r d = rs1 OP Immediate; Load rd from Memory(rs1 + Immediate); JALR ( rd = PC + 4, PC = rs1 + Immediate ) Store rs2 to Memory(rs1 + Immediate) Branch if (rs1 condition rs2) is true to Memory(PC + Immediate*2), i.e., PC = PC + Immediate*2 Upper “Long” Immediate (AUIPC, LUI): PC or rd = { imm , 12b’0} JAL to Memory (PC + Immediate*2), i.e., rd = PC + 4; PC = PC + immediate*2

6 .J-Format for Jump Instructions (JAL) JAL saves PC+4 in register rd (the return address) Assembler “ j ” jump is pseudo - instruction, uses JAL but sets rd =x0 to discard return address Set PC = PC + offset (PC-relative jump: offset = signed immediate * 2) Target somewhere within ±2 19 locations, 2 bytes apart ± 2 18 32-bit instructions, ± 2 20 bytes Immediate encoded optimized similarly to branch instruction to reduce hardware cost 6 Fall 2017 - Lecture #8 9/19/17

7 .Uses of JAL # j pseudo-instruction j Label = jal x0, Label # Discard return address # Call function within 2 18 instructions of PC jal ra , FuncName 7 Fall 2017 - Lecture #8 9/19/17

8 .JALR Instruction (I-Format) JALR rd , rs , immediate Writes PC+4 to rd (return address) Sets PC = rs + immediate (12 bit, sign extended) Uses same immediates as arithmetic and loads Unlike branches , no multiplication by two before adding to rs to form the new PC Byte offset NOT halfword offset as in branches and JAL 8 Fall 2017 - Lecture #8 9/19/17

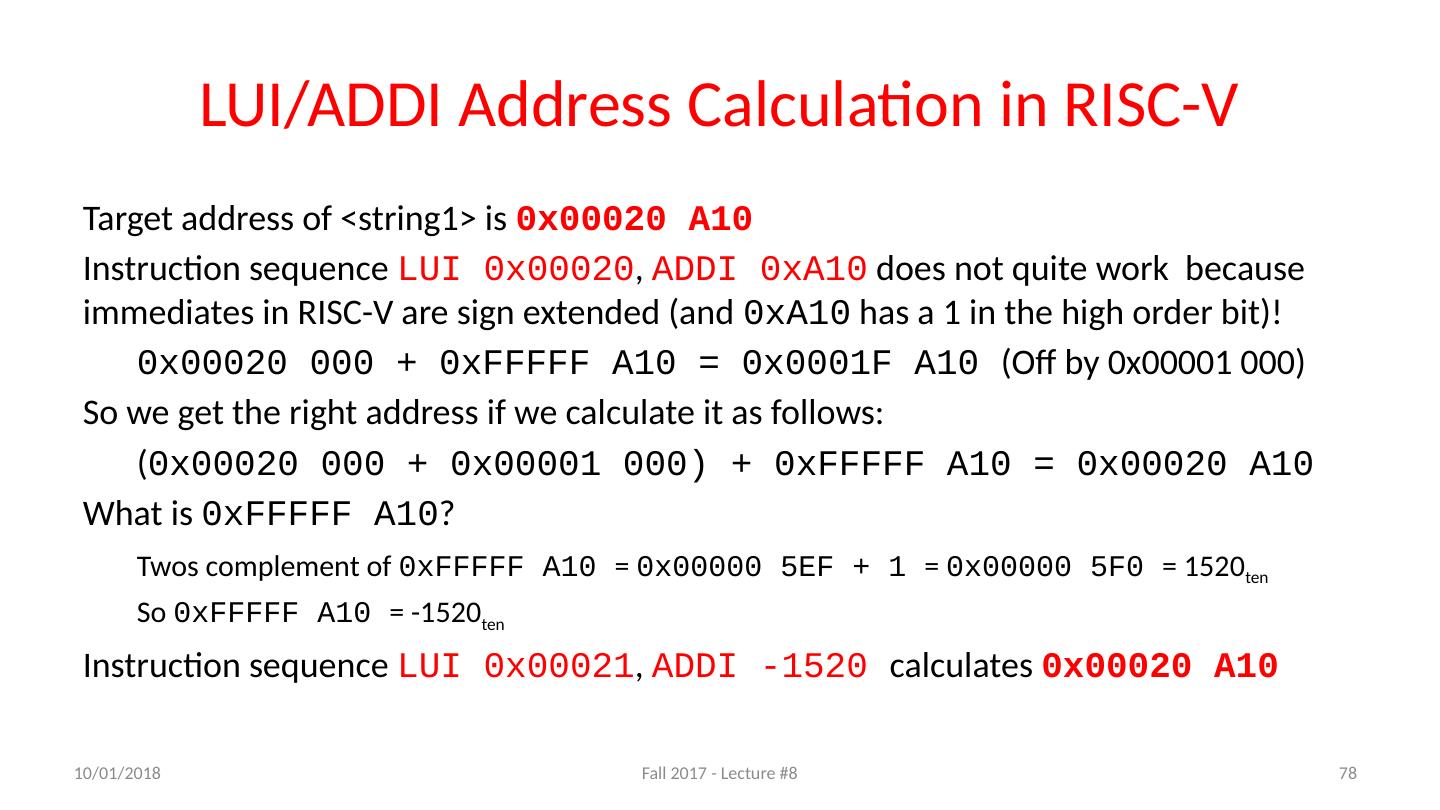

9 .Uses of JALR # ret and jr pseudo-instructions ret = jr ra = jalr x0, ra , 0 # Call function at any 32-bit absolute address lui x1, <hi20bits> jalr ra , x1, <lo12bits > # Jump PC-relative with 32-bit offset auipc x1, <hi20bits> jalr x0, x1, <lo12bits> 9 Fall 2017 - Lecture #8 9/19/17

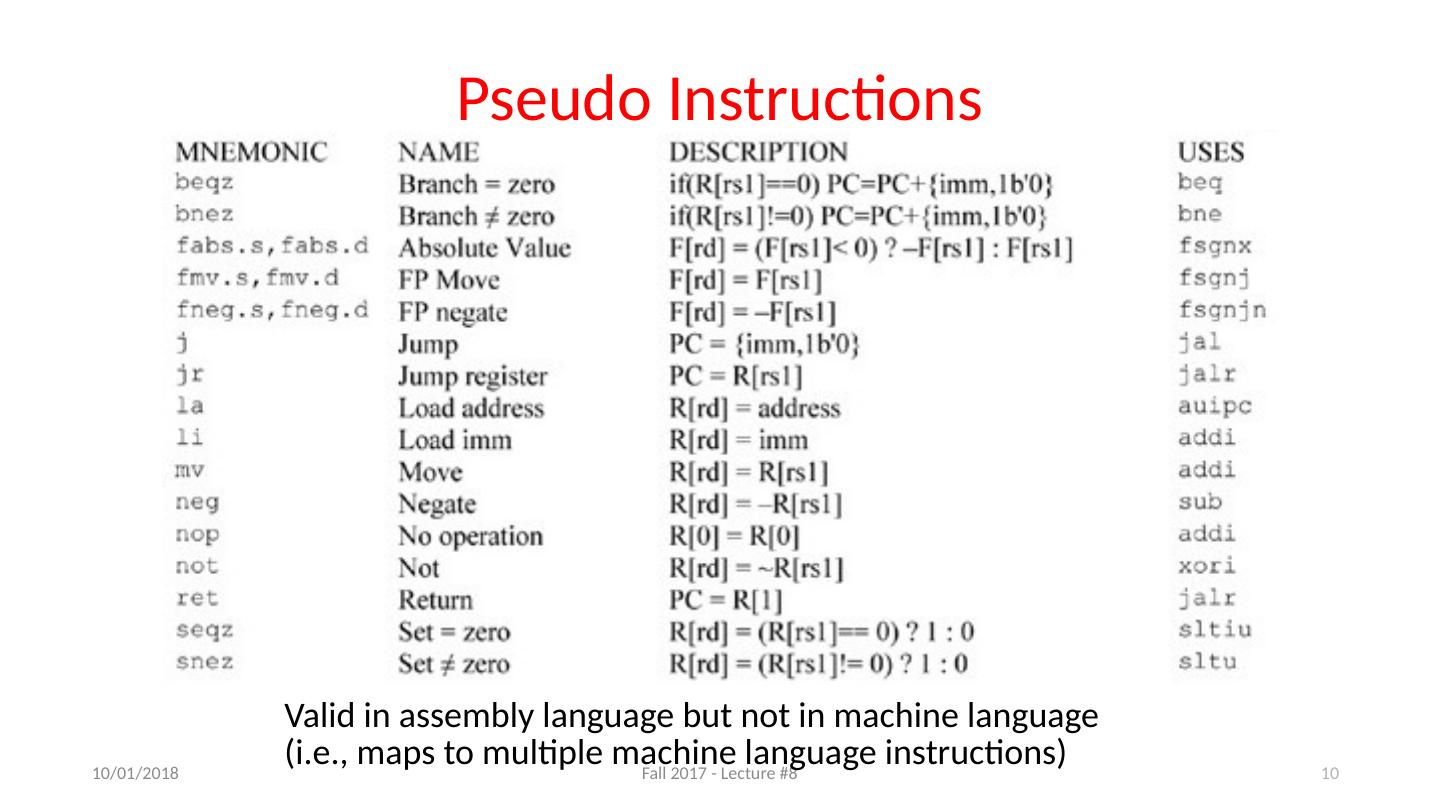

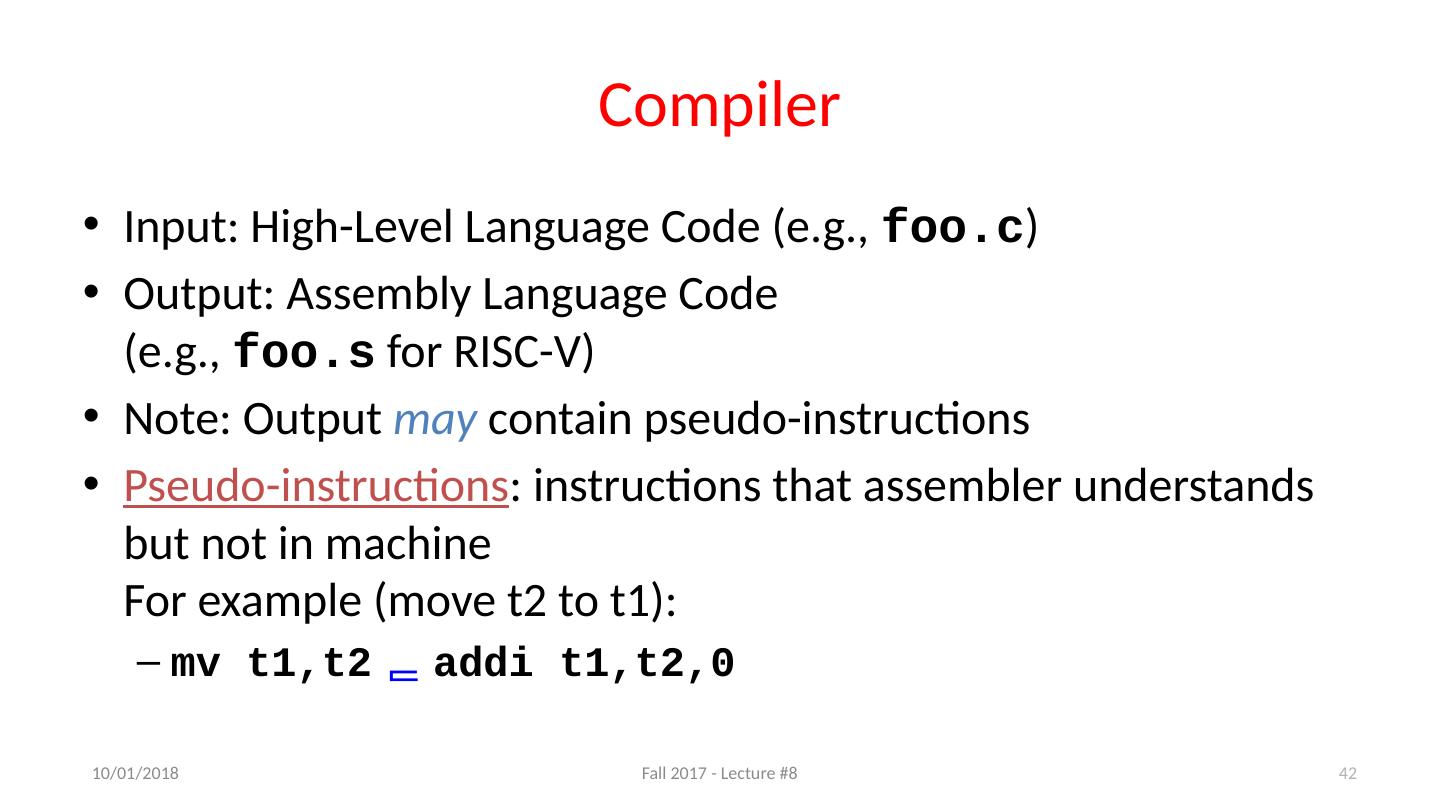

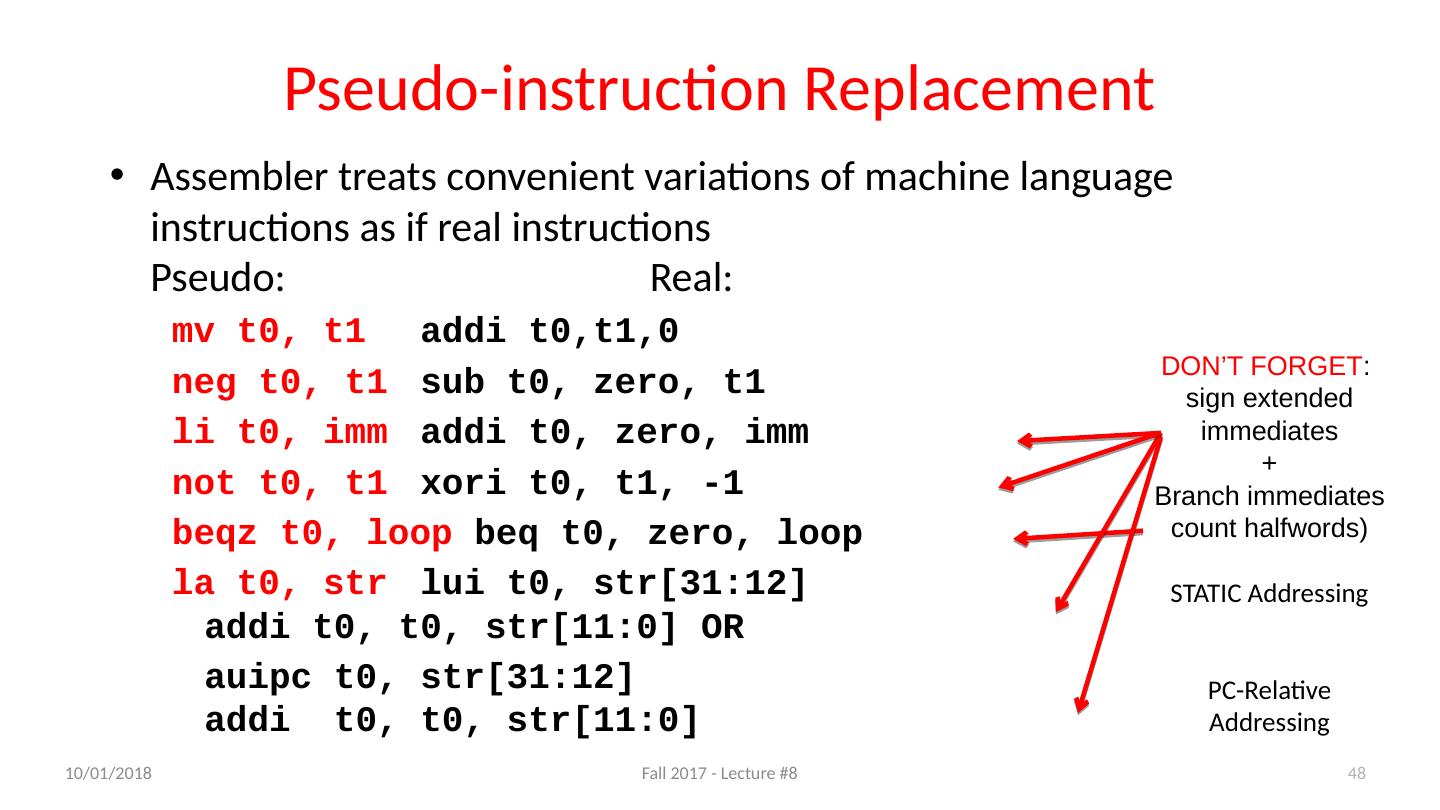

10 .Pseudo Instructions 9/19/17 Fall 2017 - Lecture # 8 10 Valid in assembly language but not in machine language (i.e., maps to multiple machine language instructions )

11 .Outline Review Instruction Formats + J/JAL Multiply and Divide Interpretation vs. Translation Assembler Linker Loader And in Conclusion … 9/19/17 Fall 2017 - Lecture #8 11

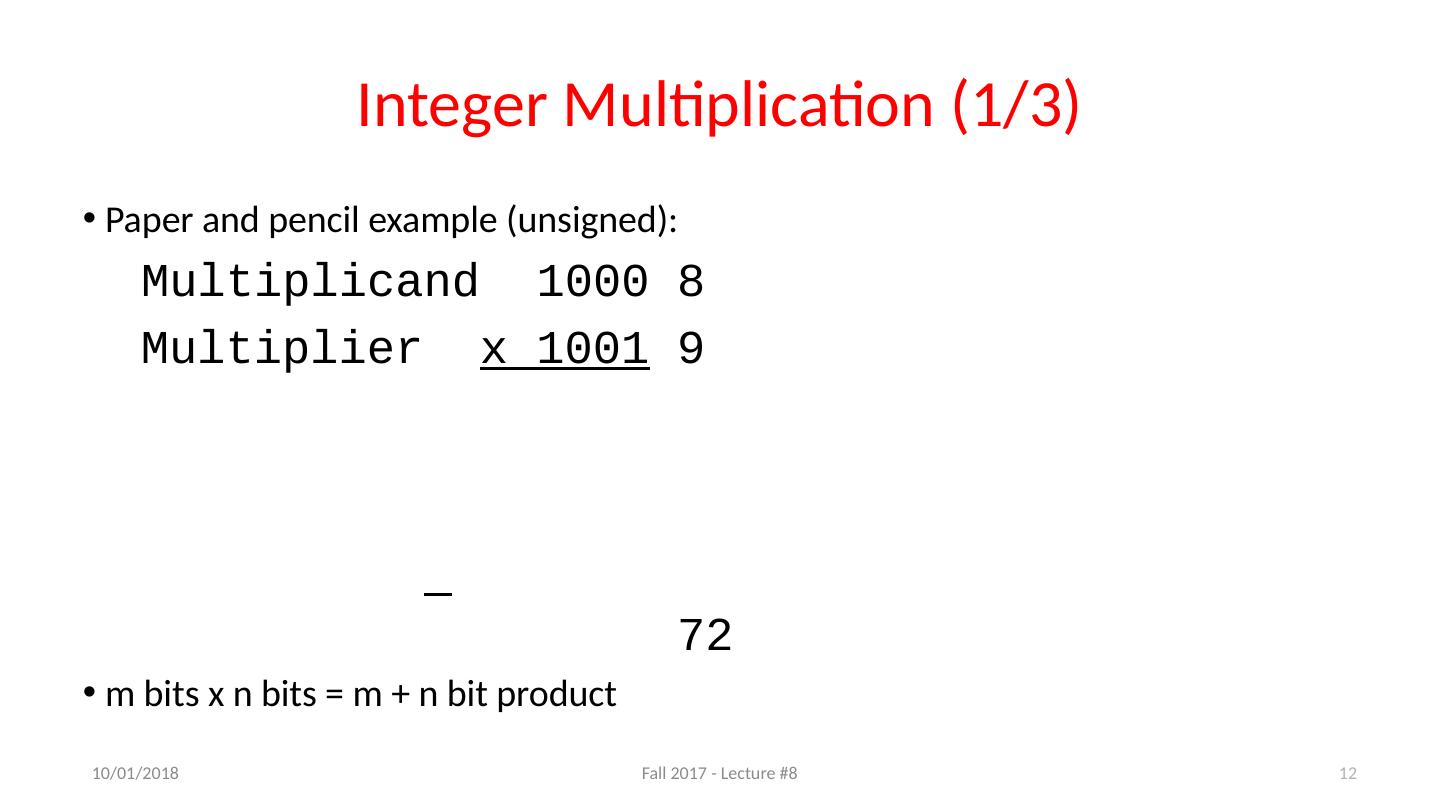

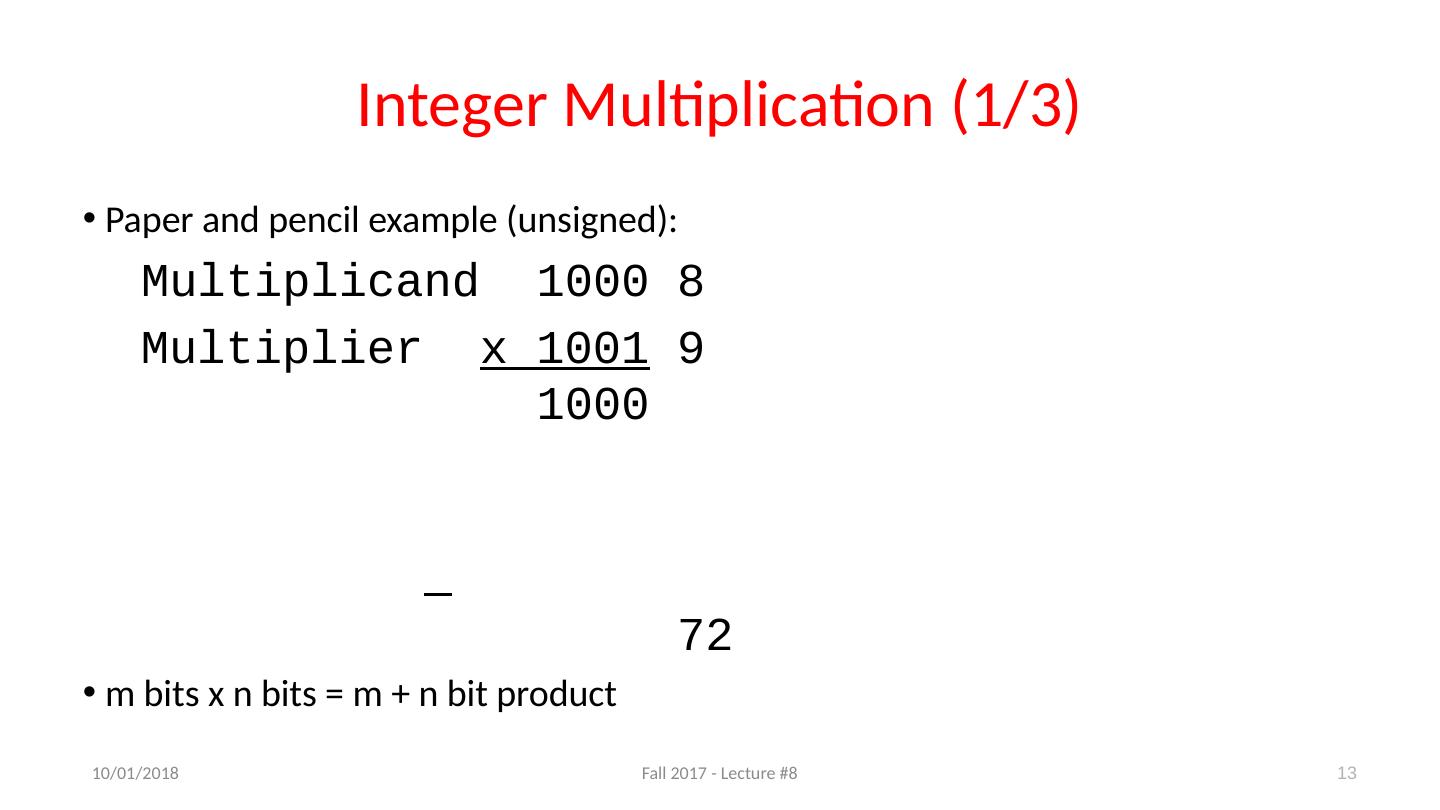

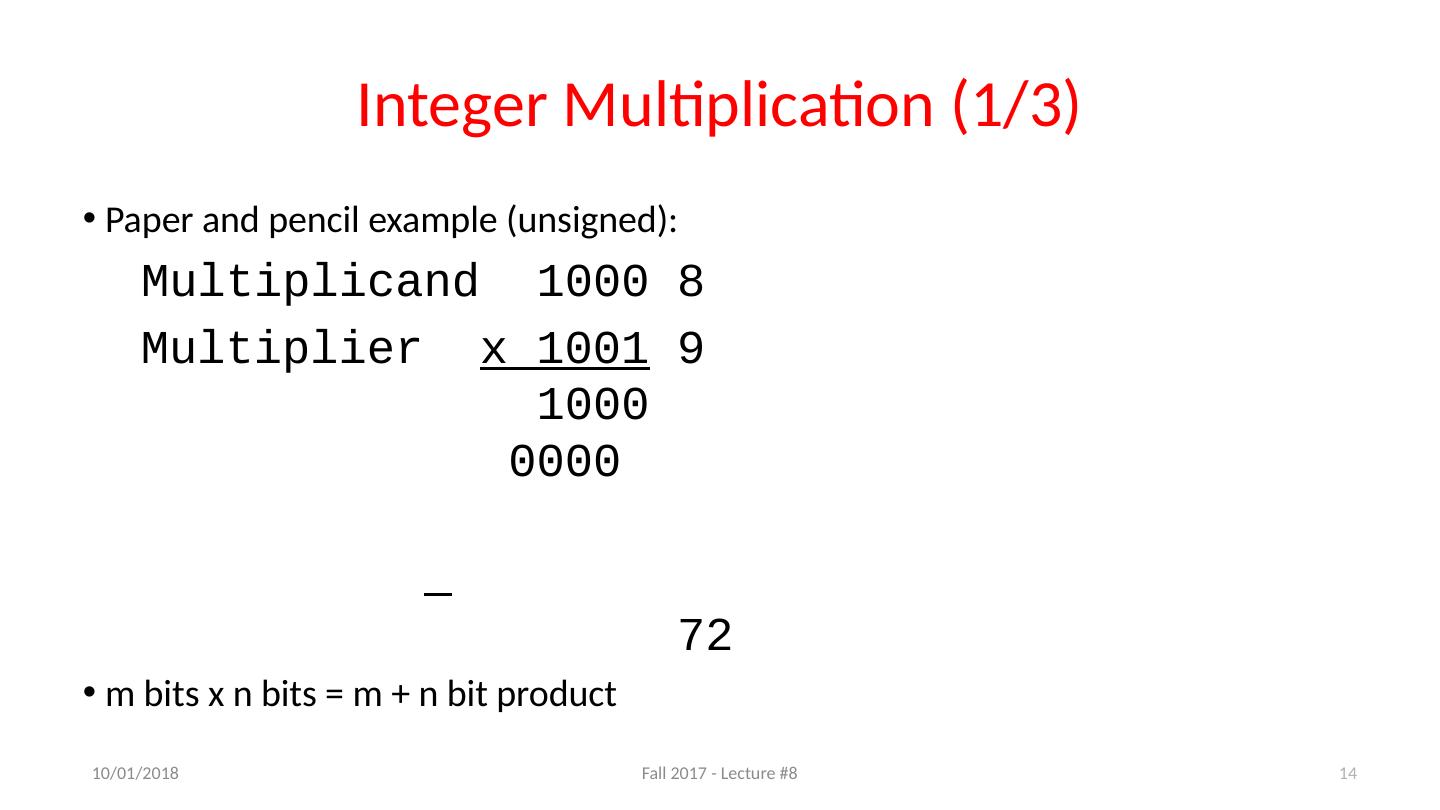

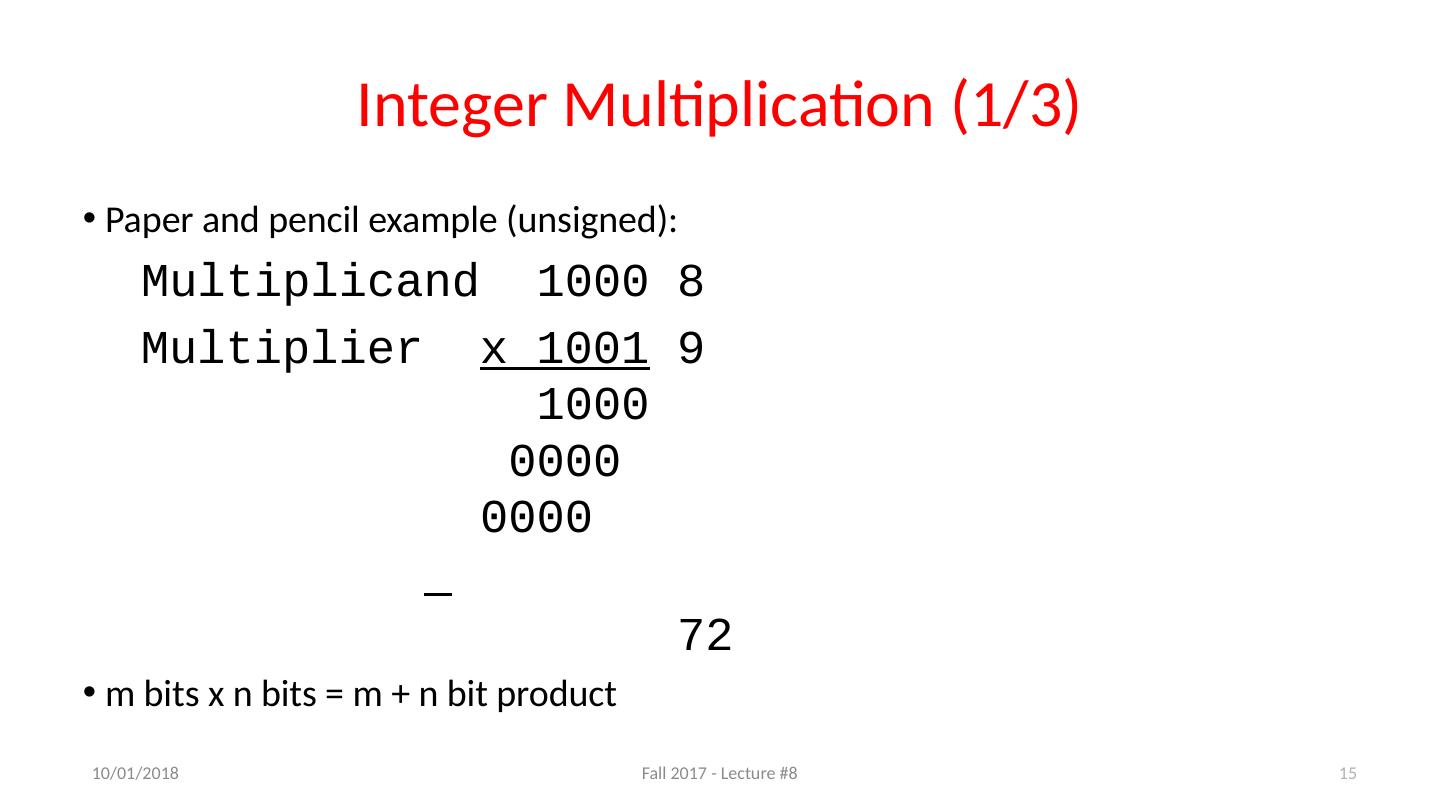

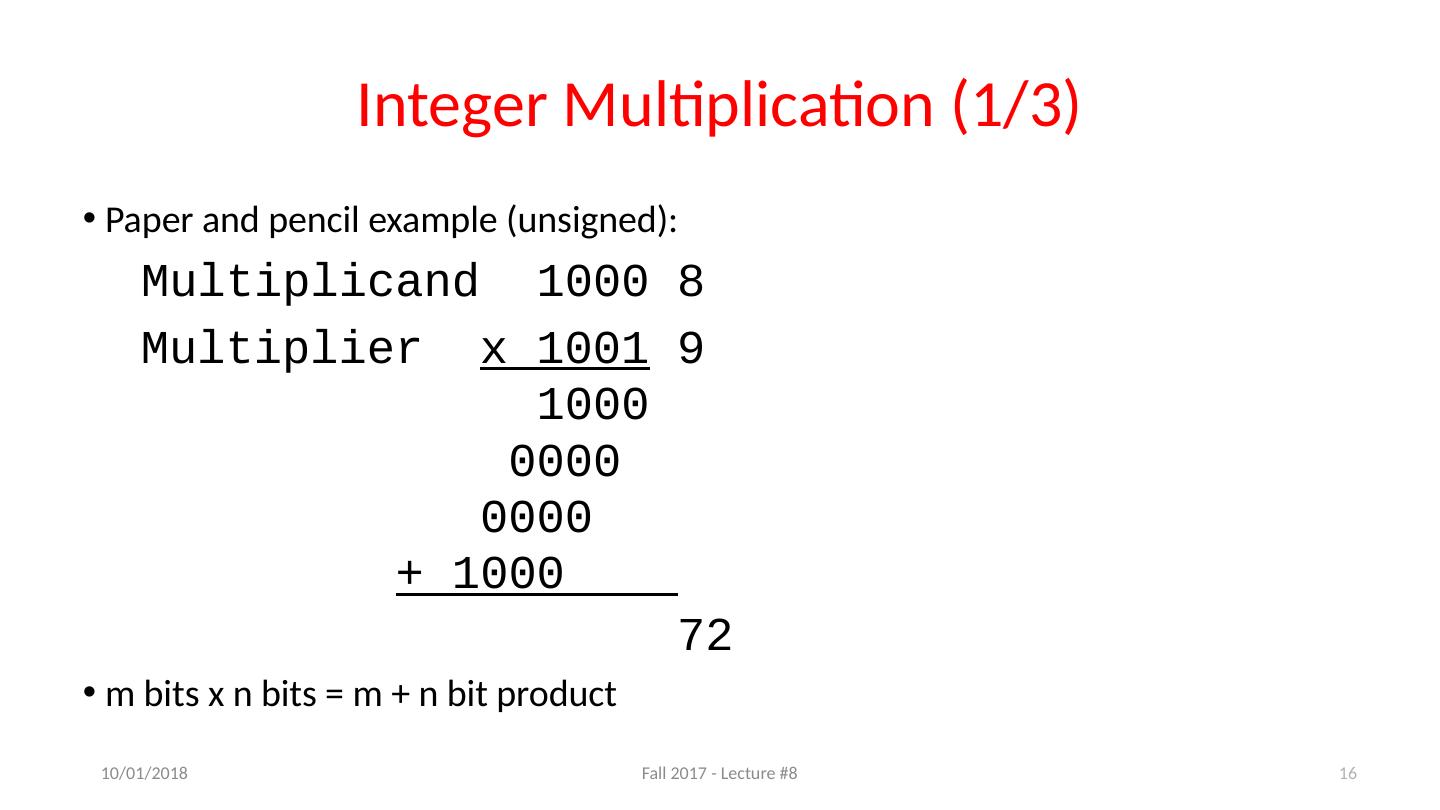

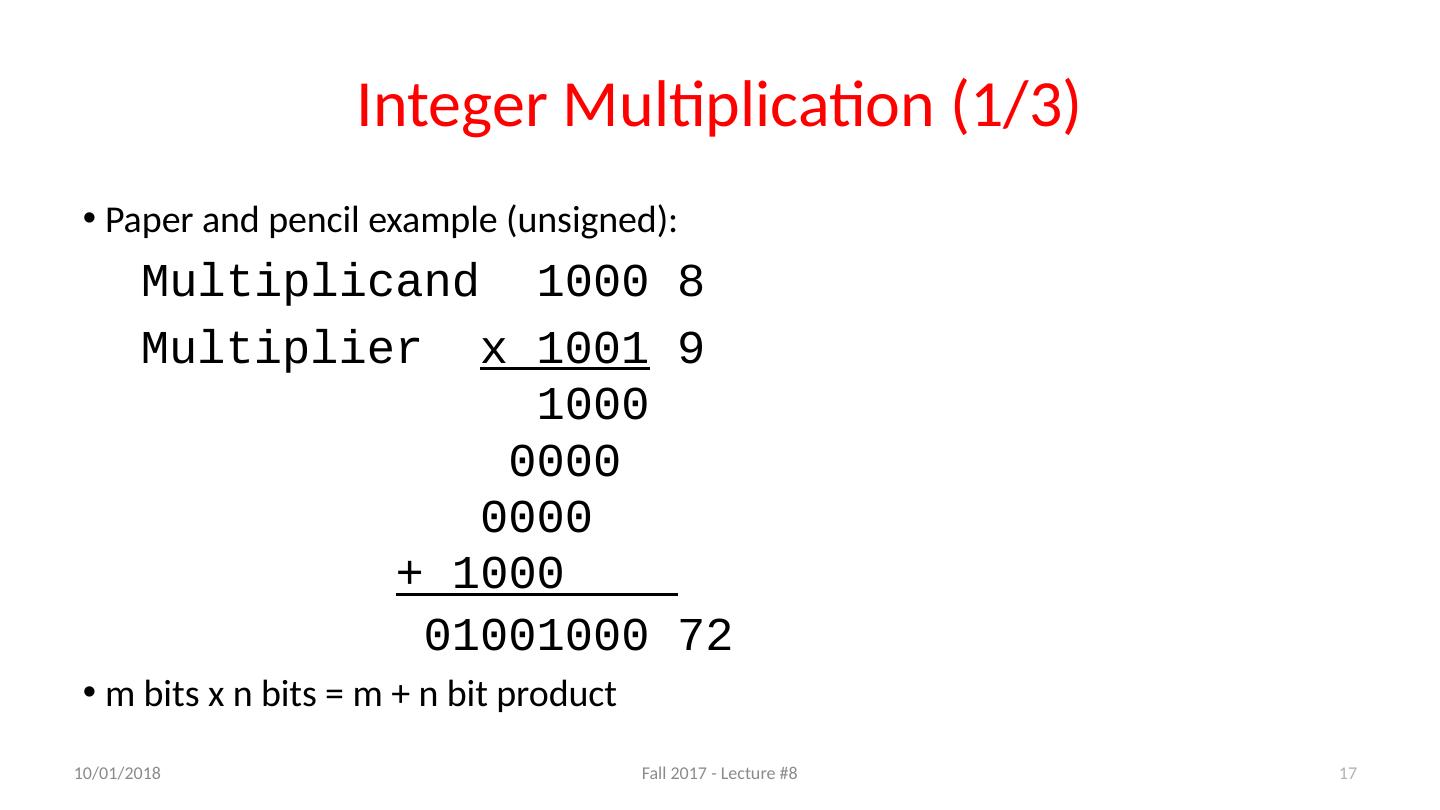

12 .Integer Multiplication (1/3) Paper and pencil example (unsigned): Multiplicand 1000 8 Multiplier x 1001 9 72 m bits x n bits = m + n bit product 12 9/19/17 Fall 2017 - Lecture #8

13 .Integer Multiplication (1/3) Paper and pencil example (unsigned): Multiplicand 1000 8 Multiplier x 1001 9 1000 72 m bits x n bits = m + n bit product 13 9/19/17 Fall 2017 - Lecture #8

14 .Integer Multiplication (1/3) Paper and pencil example (unsigned): Multiplicand 1000 8 Multiplier x 1001 9 1000 0000 72 m bits x n bits = m + n bit product 14 9/19/17 Fall 2017 - Lecture #8

15 .Integer Multiplication (1/3) Paper and pencil example (unsigned): Multiplicand 1000 8 Multiplier x 1001 9 1000 0000 0000 72 m bits x n bits = m + n bit product 15 9/19/17 Fall 2017 - Lecture #8

16 .Integer Multiplication (1/3) Paper and pencil example (unsigned): Multiplicand 1000 8 Multiplier x 1001 9 1000 0000 0000 + 1000 72 m bits x n bits = m + n bit product 16 9/19/17 Fall 2017 - Lecture #8

17 .Integer Multiplication (1/3) Paper and pencil example (unsigned): Multiplicand 1000 8 Multiplier x 1001 9 1000 0000 0000 + 1000 01001000 72 m bits x n bits = m + n bit product 17 9/19/17 Fall 2017 - Lecture #8

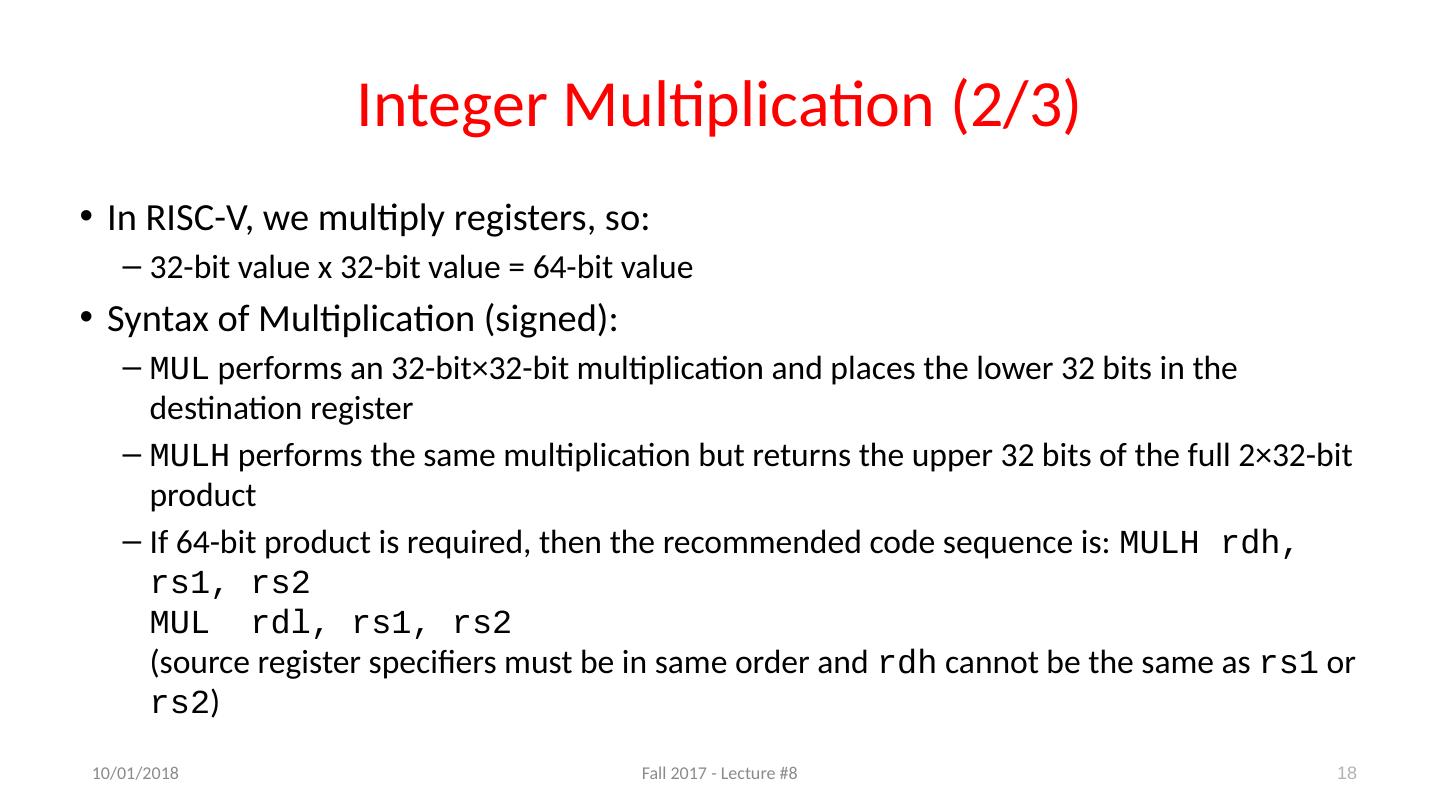

18 .Integer Multiplication (2/3) In RISC-V, we multiply registers, so: 32-bit value x 32-bit value = 64-bit value Syntax of Multiplication (signed): MUL performs an 32-bit×32-bit multiplication and places the lower 32 bits in the destination register MULH performs the same multiplication but returns the upper 32 bits of the full 2×32-bit product If 64-bit product is required , then the recommended code sequence is: MULH rdh , rs1, rs2 MUL rdl , rs1, rs2 ( source register specifiers must be in same order and rdh cannot be the same as rs1 or rs2 ) 18 9/19/17 Fall 2017 - Lecture #8

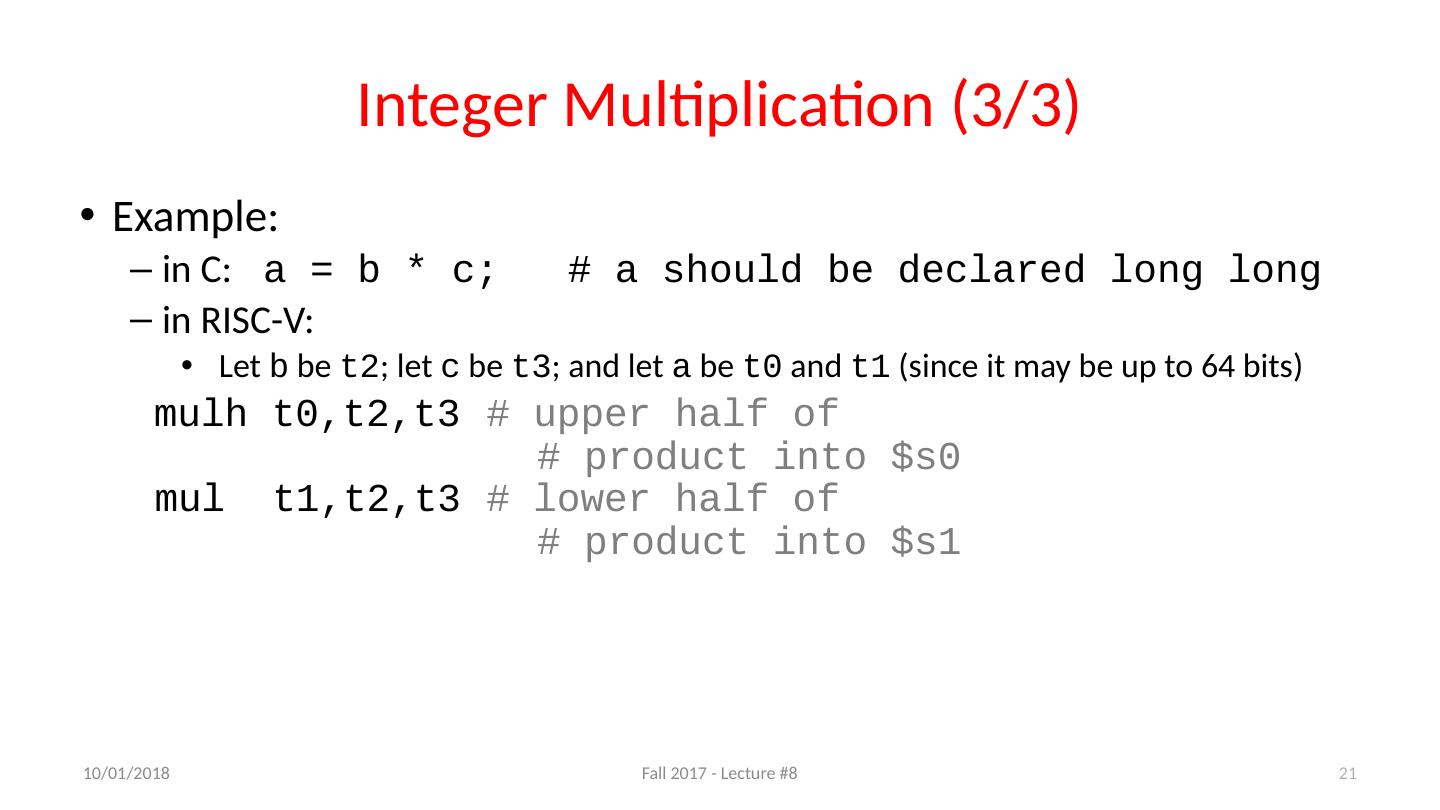

19 .Integer Multiplication (3/3) Example : in C: a = b * c ; # a should be declared long long in RISC-V: L et b be t 2 ; let c be t 3 ; and let a be t 0 and t 1 (since it may be up to 64 bits) # upper half of # product into $s0 # lower half of # product into $ s1 19 9/19/17 Fall 2017 - Lecture #8

20 .Integer Multiplication (3/3) Example : in C: a = b * c; # a should be declared long long in RISC-V: L et b be t 2 ; let c be t 3 ; and let a be t 0 and t 1 (since it may be up to 64 bits) mulh t0,t2,t3 # upper half of # product into $s0 # lower half of # product into $s1 20 9/19/17 Fall 2017 - Lecture #8

21 .Integer Multiplication (3/3) Example : in C: a = b * c ; # a should be declared long long in RISC-V: L et b be t 2 ; let c be t 3 ; and let a be t 0 and t 1 (since it may be up to 64 bits) mulh t0,t2,t3 # upper half of # product into $s0 mul t1,t2,t3 # lower half of # product into $s1 21 9/19/17 Fall 2017 - Lecture #8

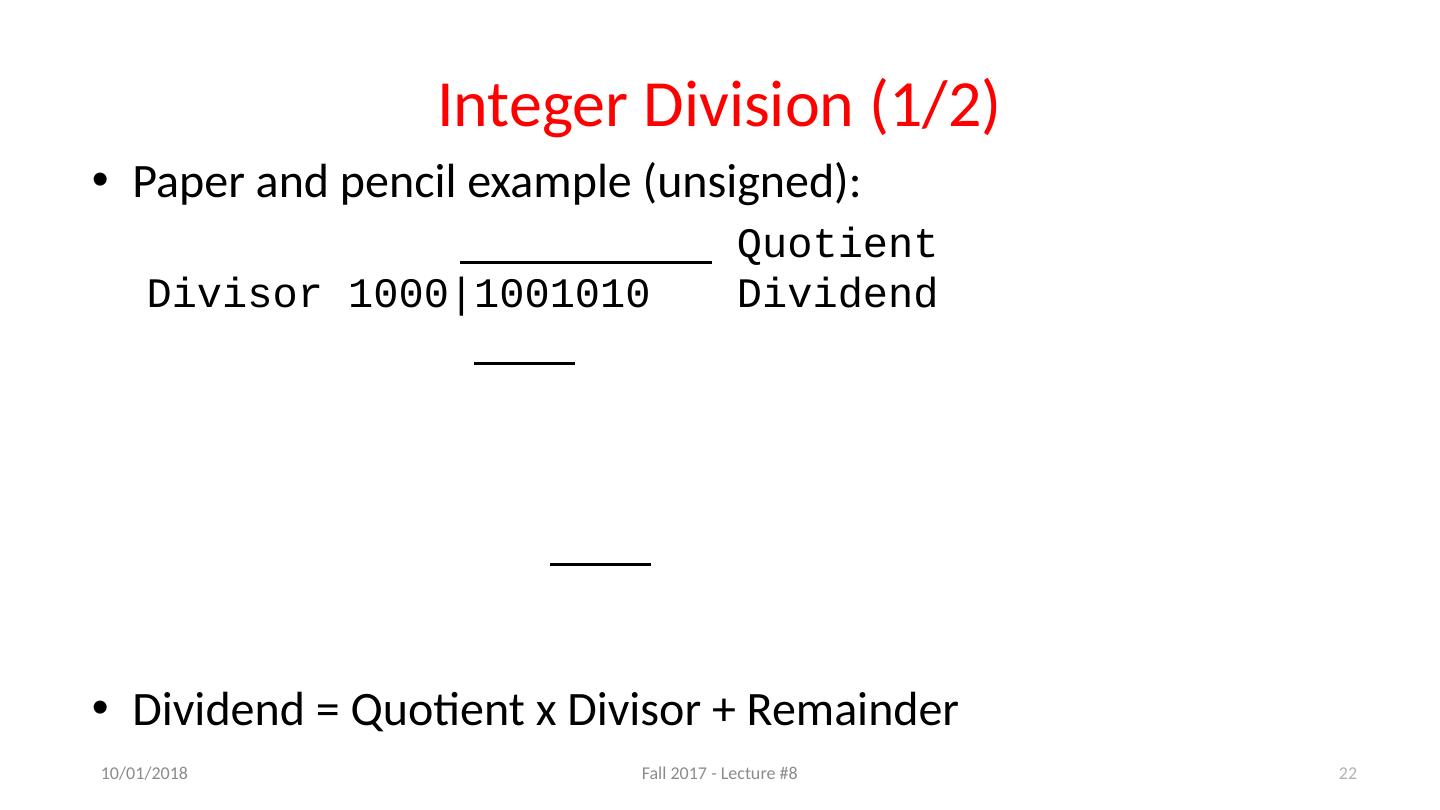

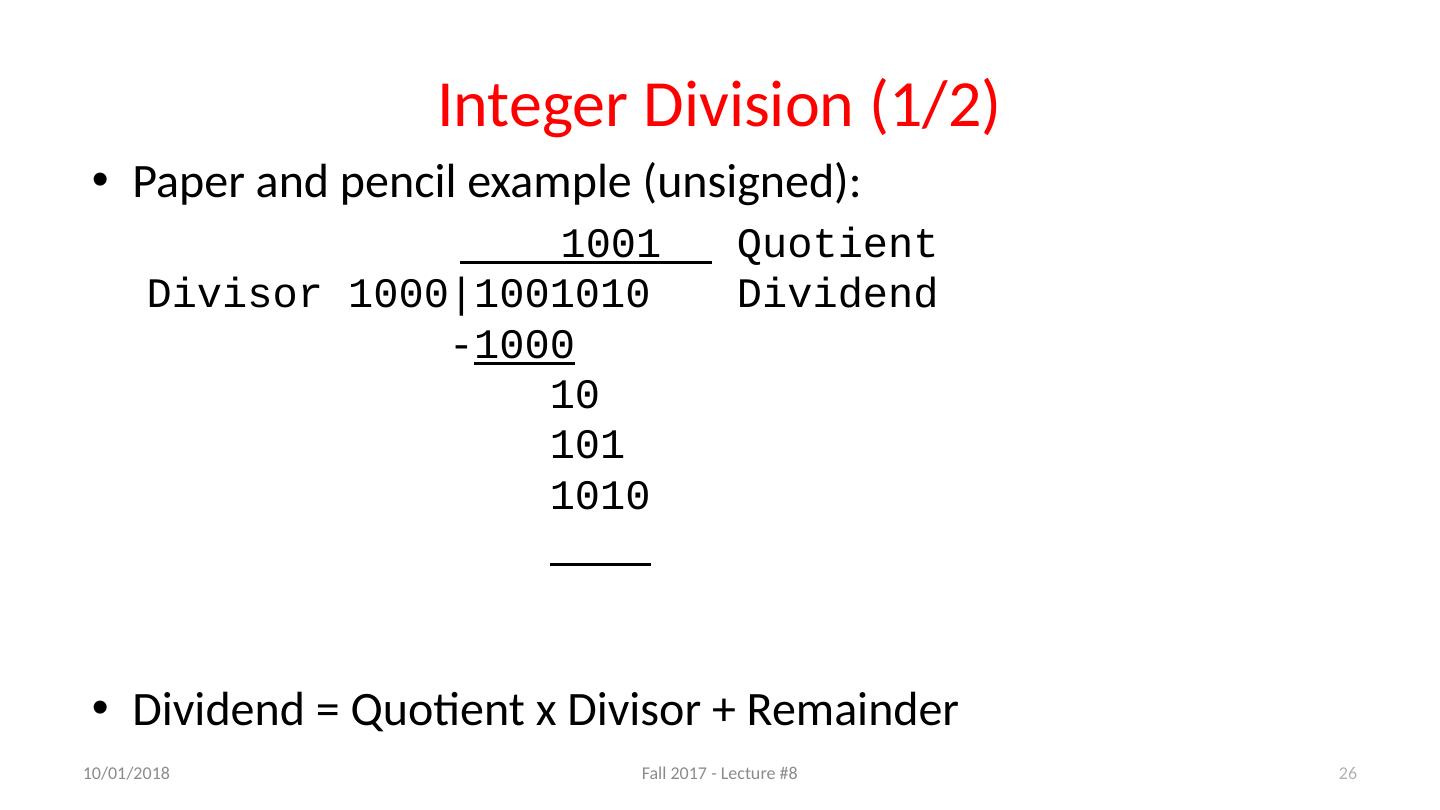

22 .Integer Division (1/2) 22 Paper and pencil example (unsigned): Quotient Divisor 1000|1001010 Dividend Dividend = Quotient x Divisor + Remainder 9/19/17 Fall 2017 - Lecture #8

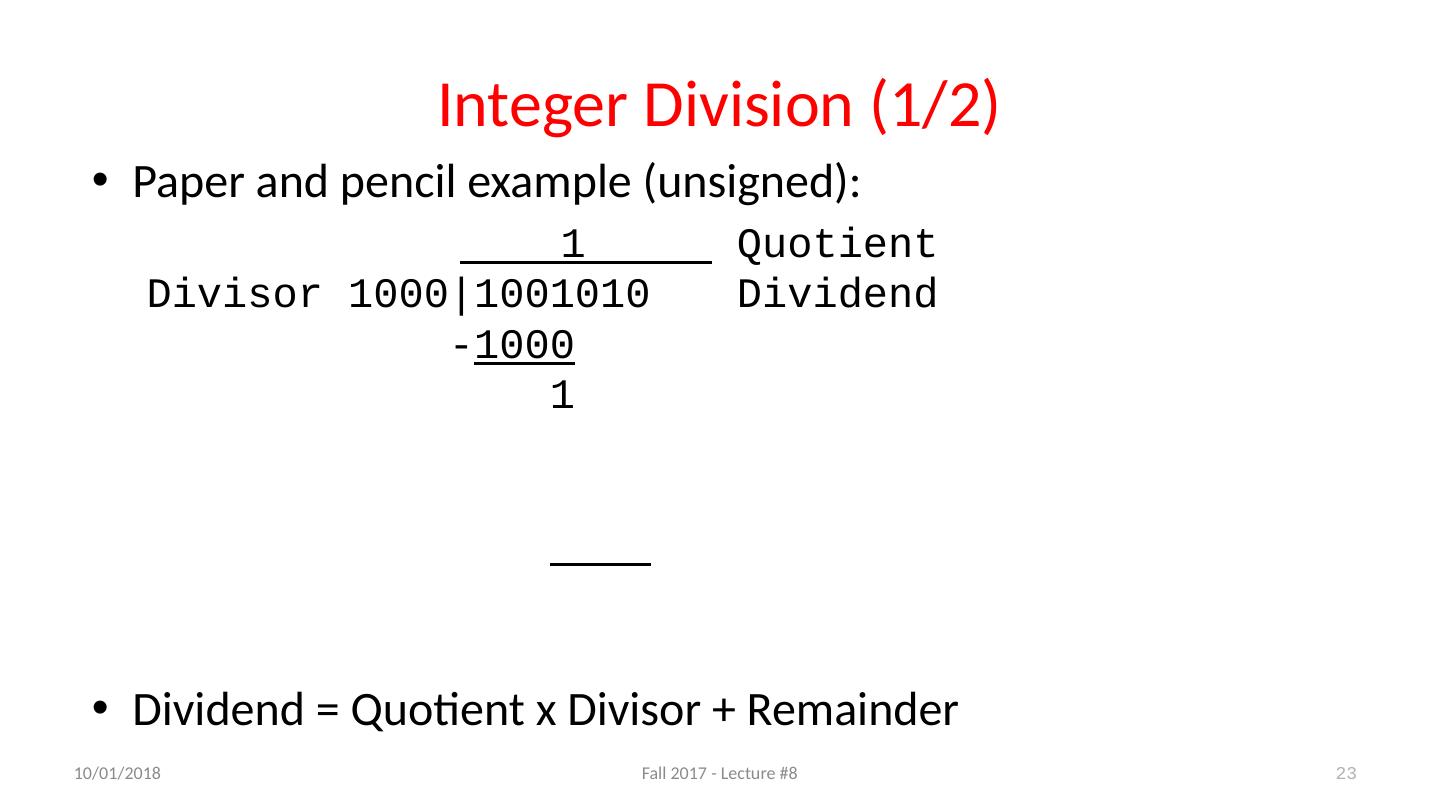

23 .Integer Division (1/2) 23 Paper and pencil example (unsigned): 1 Quotient Divisor 1000|1001010 Dividend - 1000 1 Dividend = Quotient x Divisor + Remainder 9/19/17 Fall 2017 - Lecture #8

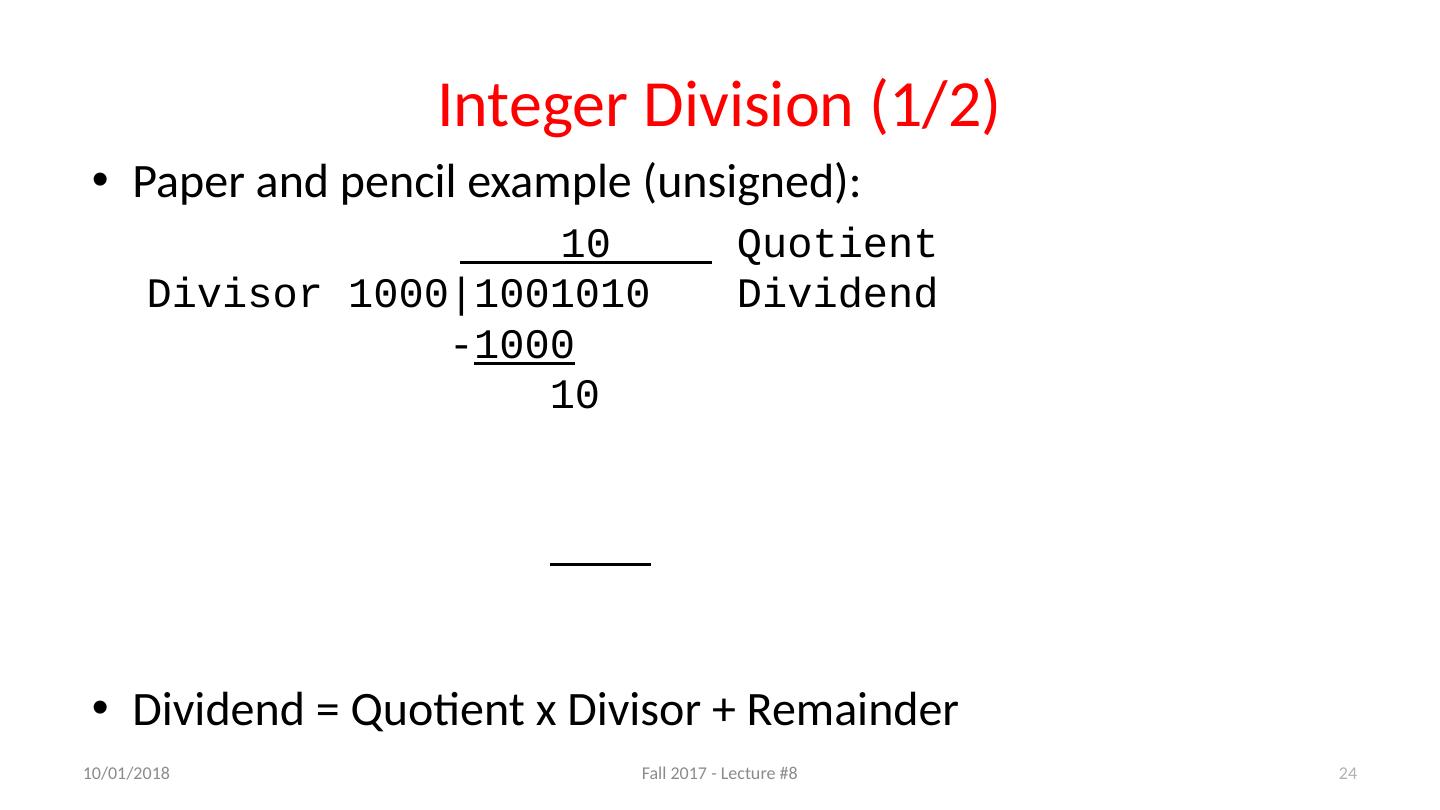

24 .Integer Division (1/2) 24 Paper and pencil example (unsigned): 10 Quotient Divisor 1000|1001010 Dividend - 1000 10 Dividend = Quotient x Divisor + Remainder 9/19/17 Fall 2017 - Lecture #8

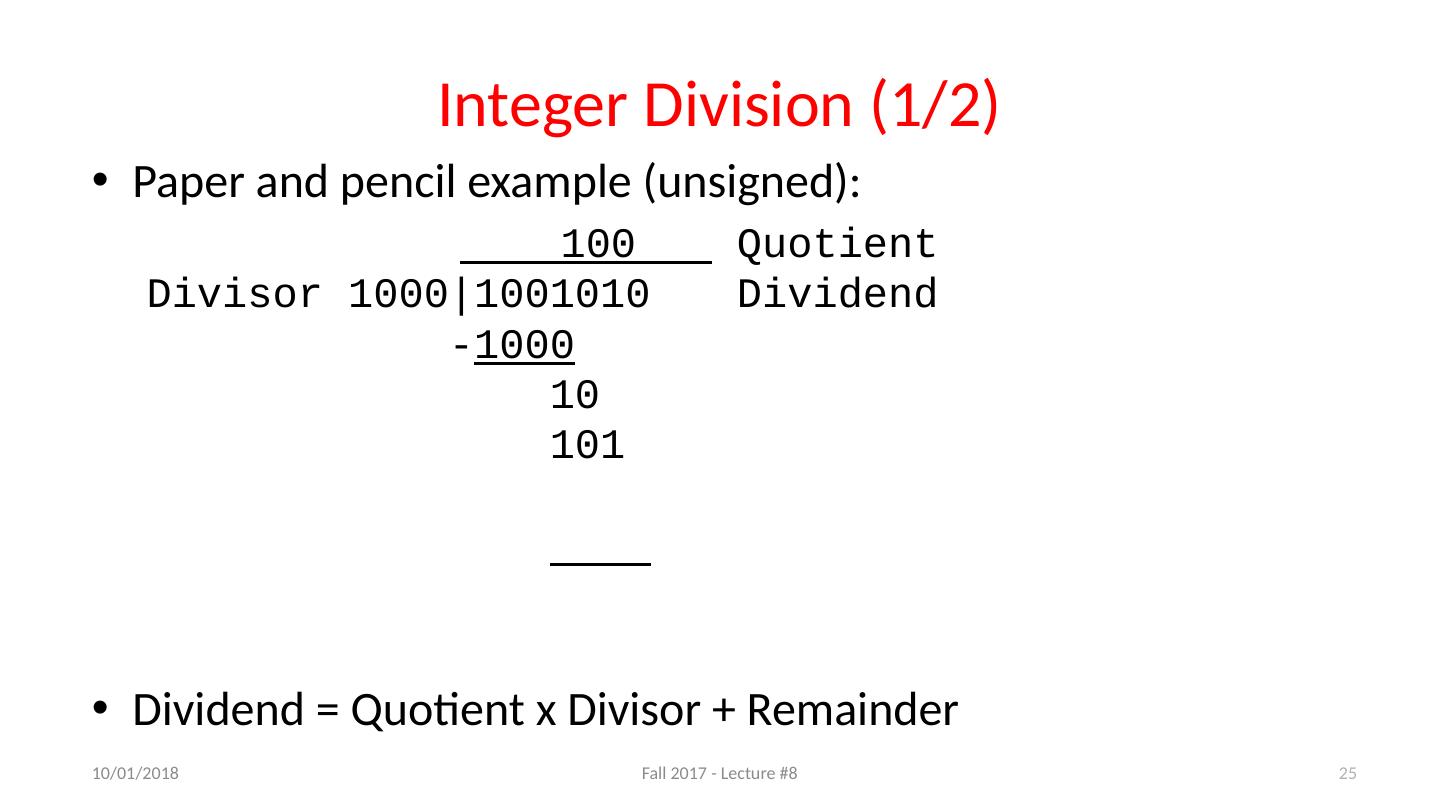

25 .Integer Division (1/2) 25 Paper and pencil example (unsigned): 100 Quotient Divisor 1000|1001010 Dividend - 1000 10 101 Dividend = Quotient x Divisor + Remainder 9/19/17 Fall 2017 - Lecture #8

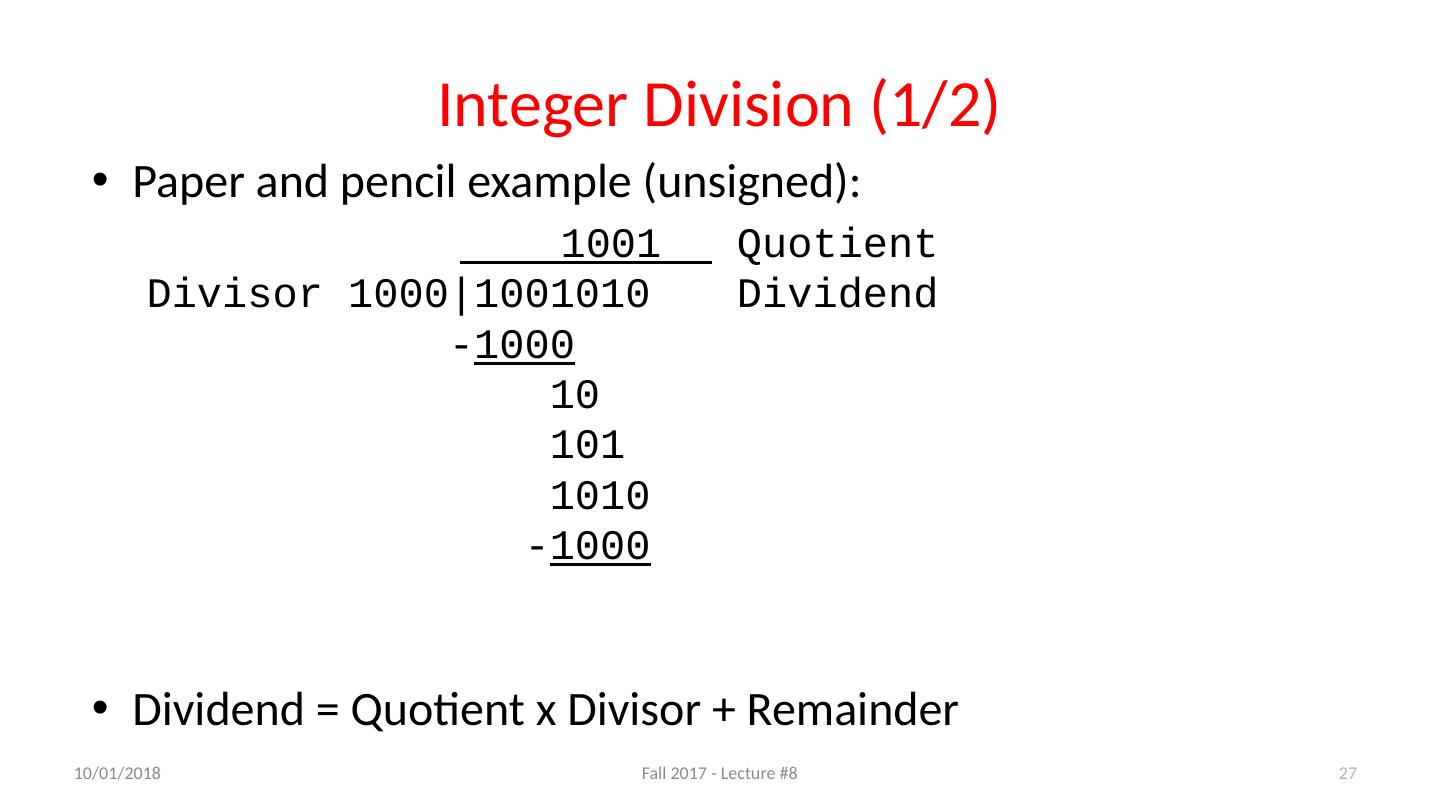

26 .Integer Division (1/2) 26 Paper and pencil example (unsigned): 1001 Quotient Divisor 1000|1001010 Dividend - 1000 10 101 1010 Dividend = Quotient x Divisor + Remainder 9/19/17 Fall 2017 - Lecture #8

27 .Integer Division (1/2) 27 Paper and pencil example (unsigned): 1001 Quotient Divisor 1000|1001010 Dividend - 1000 10 101 1010 - 1000 Dividend = Quotient x Divisor + Remainder 9/19/17 Fall 2017 - Lecture #8

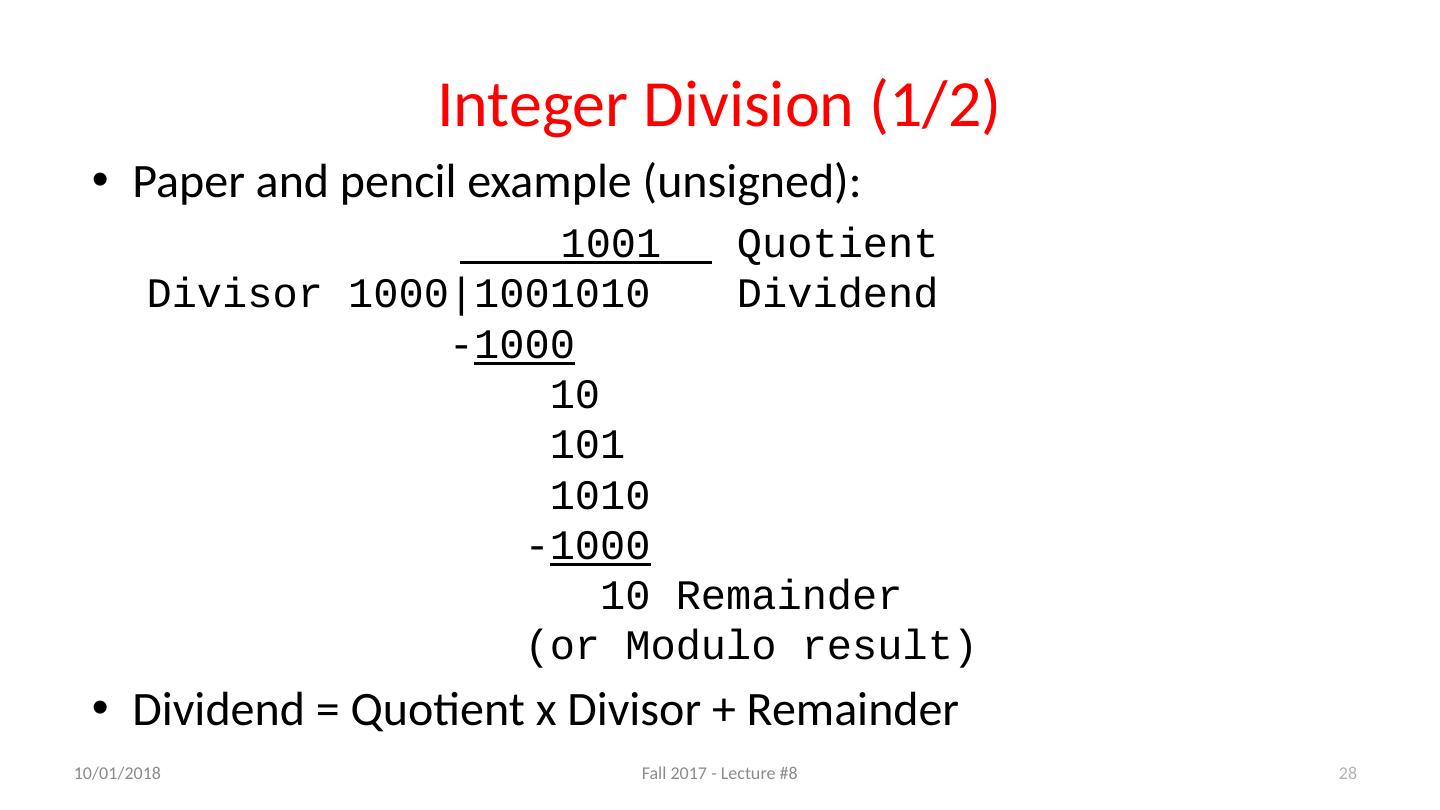

28 .Integer Division (1/2) 28 Paper and pencil example (unsigned): 1001 Quotient Divisor 1000|1001010 Dividend - 1000 10 101 1010 - 1000 10 Remainder ( or Modulo result) Dividend = Quotient x Divisor + Remainder 9/19/17 Fall 2017 - Lecture #8

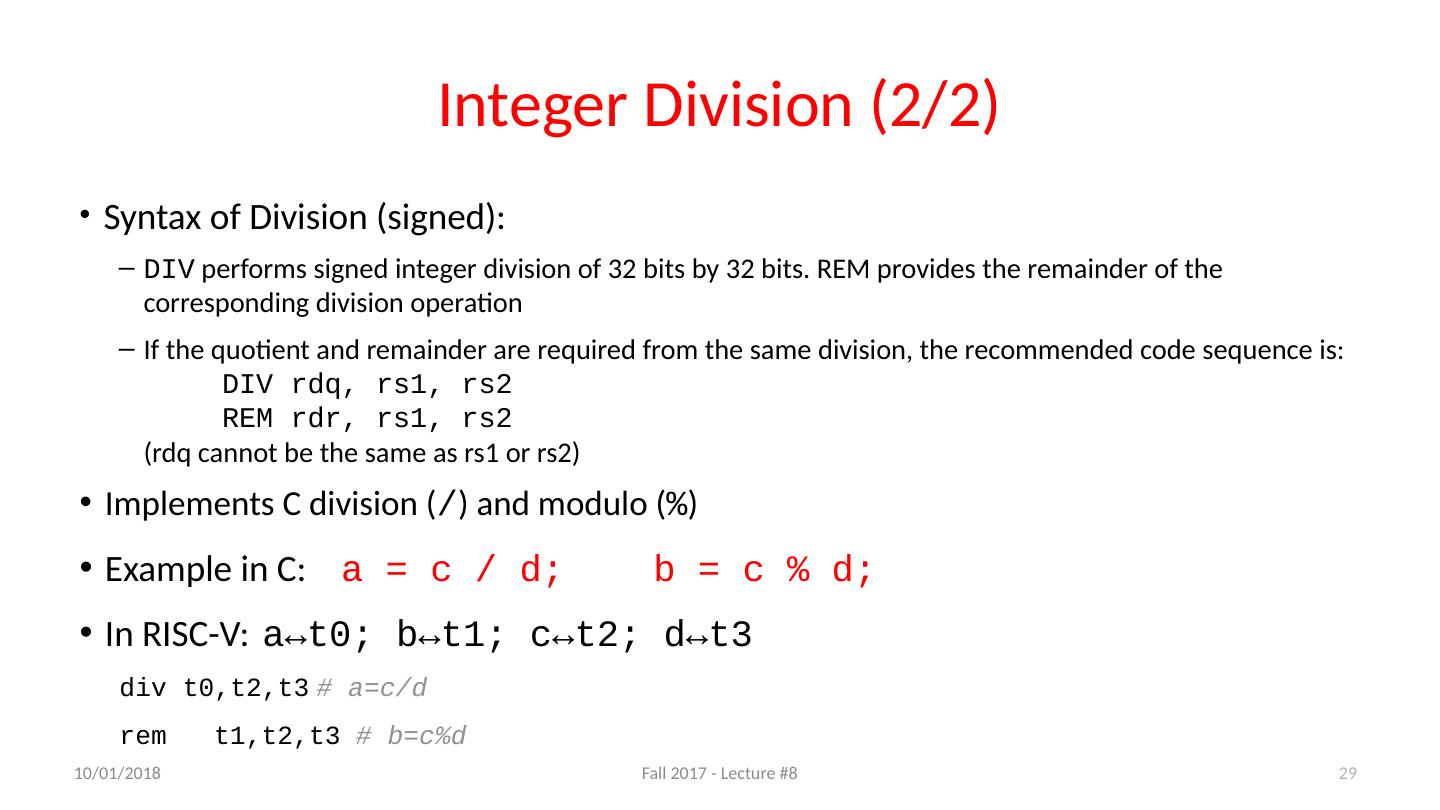

29 .Integer Division (2/2) Syntax of Division (signed): DIV performs signed integer division of 32 bits by 32 bits . REM provides the remainder of the corresponding division operation If the quotient and remainder are required from the same division, the recommended code sequence is: DIV rdq , rs1, rs2 REM rdr , rs1, rs2 ( rdq cannot be the same as rs1 or rs2 ) Implements C division ( / ) and modulo ( % ) Example in C: a = c / d; b = c % d; In RISC-V: a↔ t 0 ; b ↔ t 1 ; c ↔ t 2 ; d ↔ t 3 div t0,t2,t3 # a=c/d rem t1,t2,t3 # b= c%d 29 9/19/17 Fall 2017 - Lecture #8