- 快召唤伙伴们来围观吧

- 微博 QQ QQ空间 贴吧

- 文档嵌入链接

- 复制

- 微信扫一扫分享

- 已成功复制到剪贴板

汇编语言和RISCV

展开查看详情

1 .CS 61C: Great Ideas in Computer Architecture Introduction to Assembly Language and RISC-V Instruction Set Architecture Instructors: Krste Asanović & Randy H. Katz http://inst.eecs.Berkeley.edu/~cs61c 9/7/17 Fall 2017 - Lecture #5 1

2 .Outline Assembly Language RISC-V Architecture Registers vs. Variables RISC-V Instructions C-to-RISC-V Patterns And in Conclusion … 9/7/17 2

3 .Outline Assembly Language RISC-V Architecture Registers vs. Variables RISC-V Instructions C-to-RISC-V Patterns And in Conclusion … 9/7/17 3

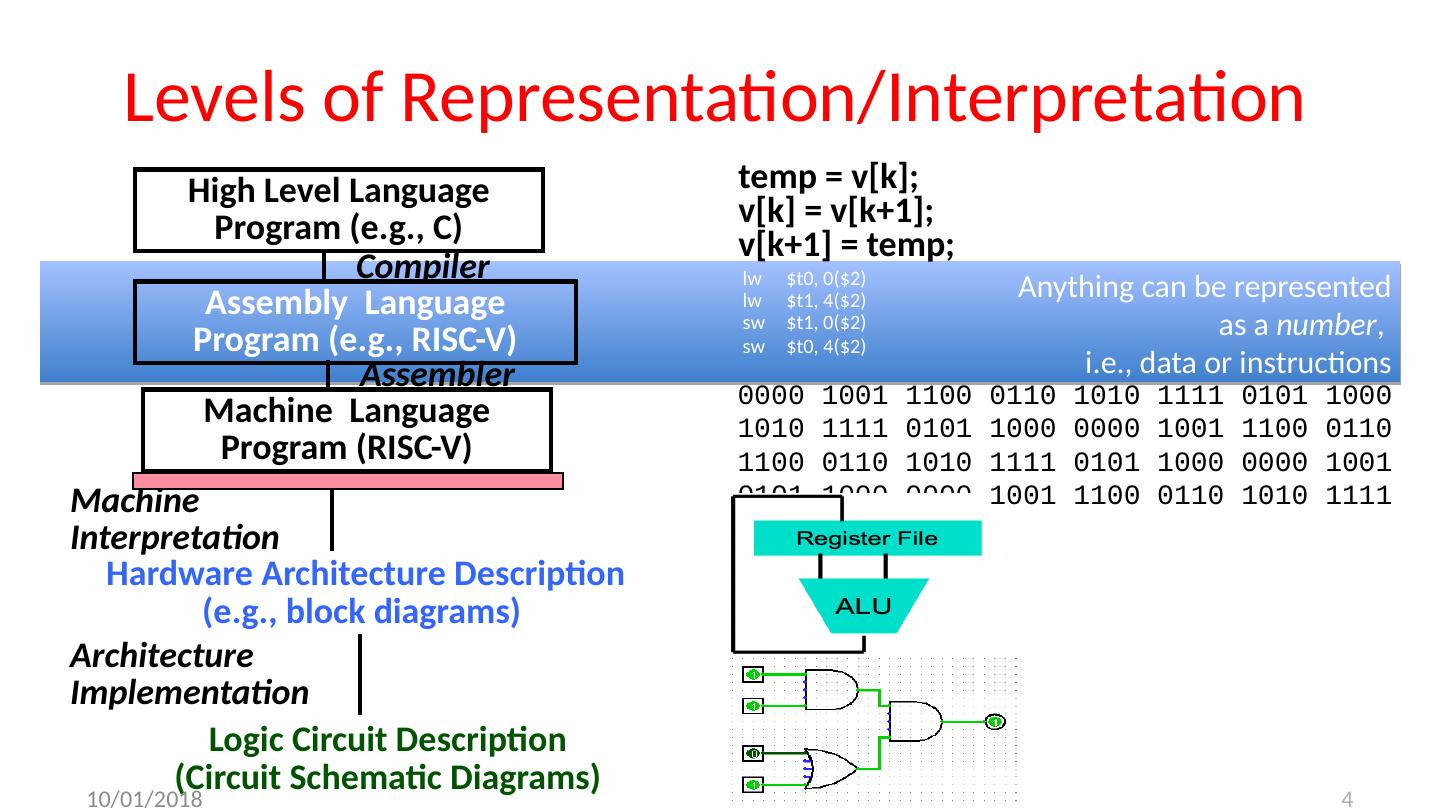

4 .Levels of Representation/Interpretation lw $t0, 0($2) lw $t1, 4($2) sw $t1, 0($2) sw $t0, 4($2) High Level Language Program (e.g., C) Assembly Language Program ( e.g., RISC-V) Machine Language Program (RISC-V) Hardware Architecture Description ( e.g., block diagrams) Compiler Assembler Machine Interpretation temp = v[k ]; v[k ] = v[k+1]; v[k+1] = temp; 0000 1001 1100 0110 1010 1111 0101 1000 1010 1111 0101 1000 0000 1001 1100 0110 1100 0110 1010 1111 0101 1000 0000 1001 0101 1000 0000 1001 1100 0110 1010 1111 Architecture Implementation Anything can be represented as a number , i.e., data or instructions Logic Circuit Description (Circuit Schematic Diagrams) 9/7/17 4

5 .Instruction Set Architecture (ISA) Job of a CPU ( Central Processing Unit , aka Core ): execute instructions Instructions: CPU’s primitives operations Like a sentence: operations (verbs) applied to operands (objects) processed in sequence … With additional operations to change the sequence CPUs belong to “families,” each implementing its own set of instructions CPU’s particular set of instructions implements an Instruction Set Architecture ( ISA ) Examples: ARM, Intel x86, MIPS, RISC-V, IBM/Motorola PowerPC (old Mac), Intel IA64, ... 5 9/7/17

6 .Assembly Language High-Level Language 6 9/7/17

7 .Assembly Language High-Level Language 7 9/7/17

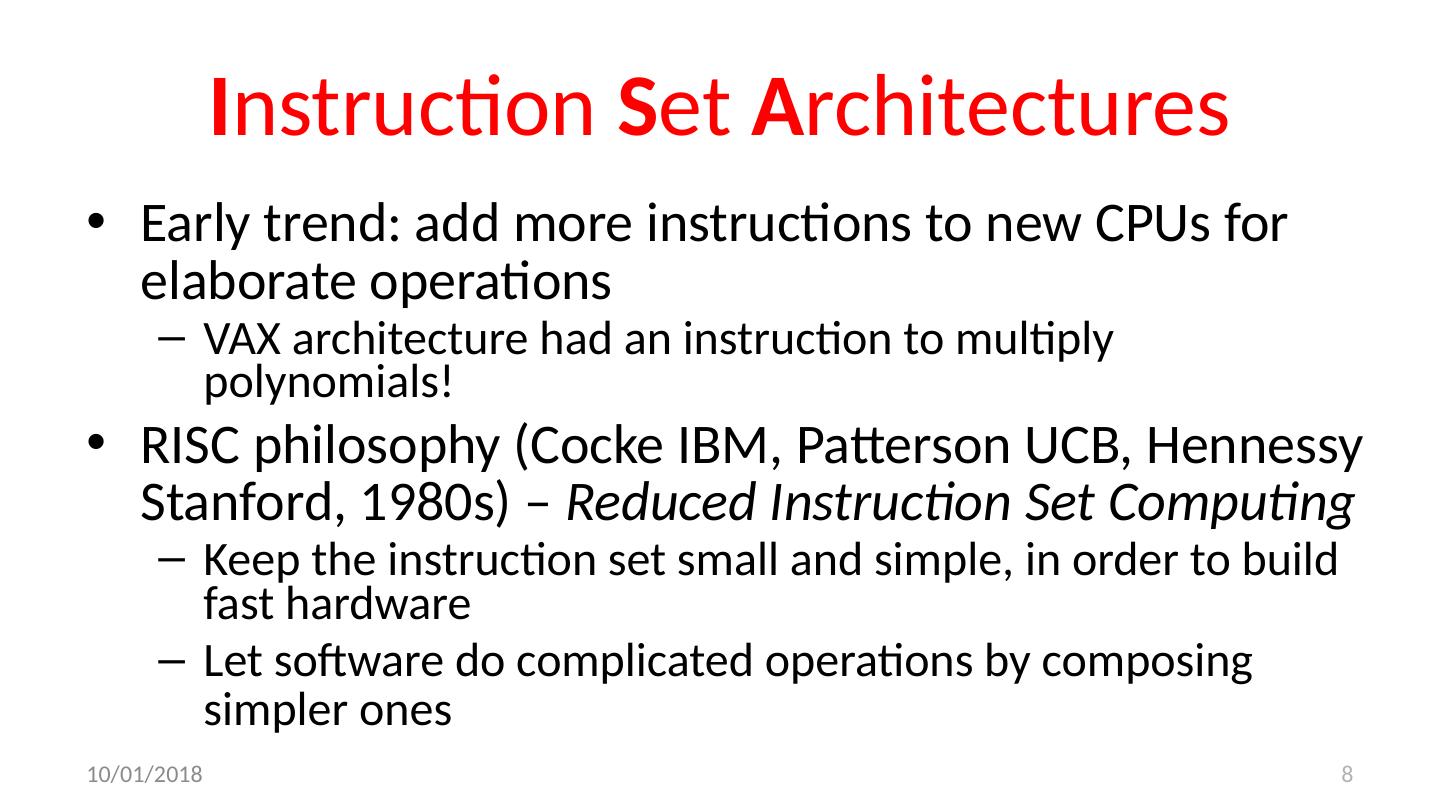

8 .I nstruction S et A rchitectures Early trend: add more instructions to new CPUs for elaborate operations VAX architecture had an instruction to multiply polynomials ! RISC philosophy ( Cocke IBM, Patterson UCB, Hennessy Stanford, 1980s) – Reduced Instruction Set Computing Keep the instruction set small and simple, in order to build fast hardware Let software do complicated operations by composing simpler ones 8 9/7/17

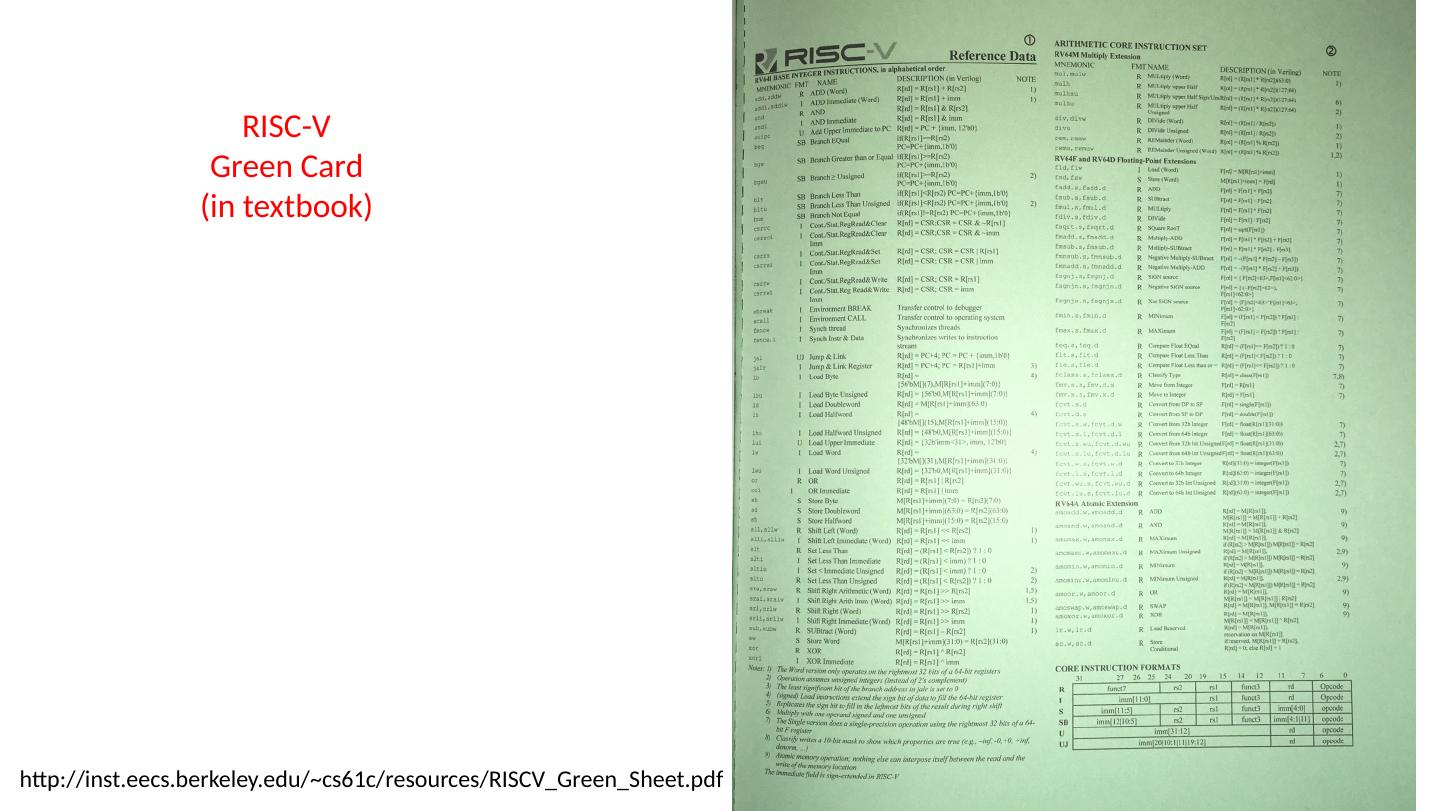

9 .RISC-V Green Card (in textbook) 9 9/7/17 http:// inst.eecs.berkeley.edu /~cs61c/resources / RISCV_Green_Sheet.pdf

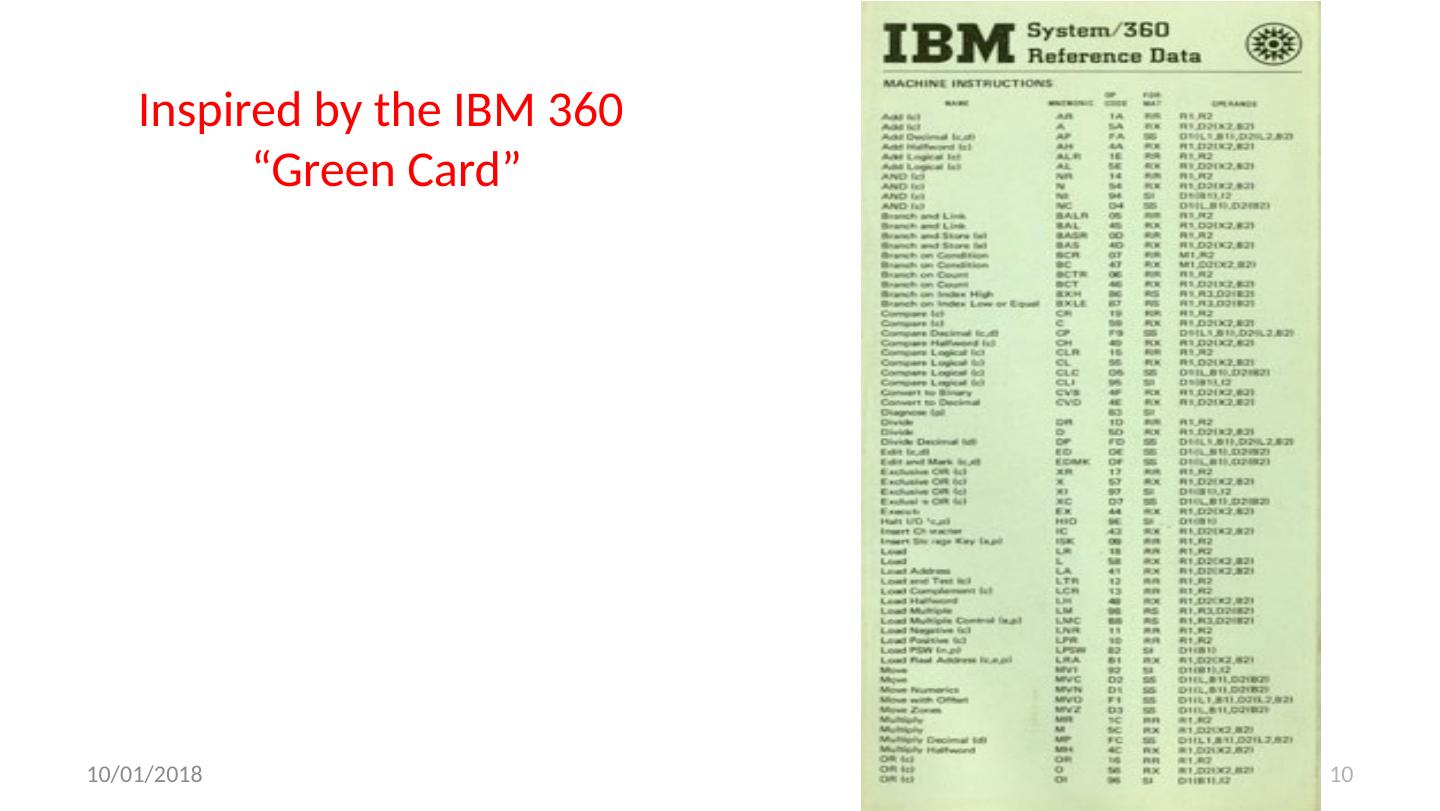

10 .Inspired by the IBM 360 “Green Card” 10 9/7/17

11 .Outline Assembly Language RISC-V Architecture Registers vs. Variables RISC-V Instructions C-to-RISC-V Patterns And in Conclusion … 9/7/17 11

12 .What is RISC-V? Fifth generation of RISC design from UC Berkeley A high-quality, license-free, royalty-free RISC ISA specification Experiencing rapid uptake in both industry and academia Both proprietary and open-source core implementations Supported by growing shared software ecosystem Appropriate for all levels of computing system, from microcontrollers to supercomputers 32-bit, 64-bit, and 128-bit variants (we’re using 32-bit in class, textbook uses 64-bit) S tandard maintained by non-profit RISC-V Foundation 12 9/7/17

13 .Foundation Members (60+) 13 Rumble Development Platinum: Gold, Silver, Auditors:

14 .Outline Assembly Language RISC-V Architecture Registers vs. Variables RISC-V Instructions C-to-RISC-V Patterns And in Conclusion … 9/7/17 14

15 .Assembly Variables: Registers Unlike HLL like C or Java, assembly does not have variables as you know and love them More primitive, closer what simple hardware can directly support Assembly operands are objects called registers Limited number of special places to hold values, built directly into the hardware Operations can only be performed on these! Benefit : Since registers are directly in hardware, they are very fast ( faster than 1 ns - light travels 1 foot in 1 ns!! ! ) 9/7/17 15

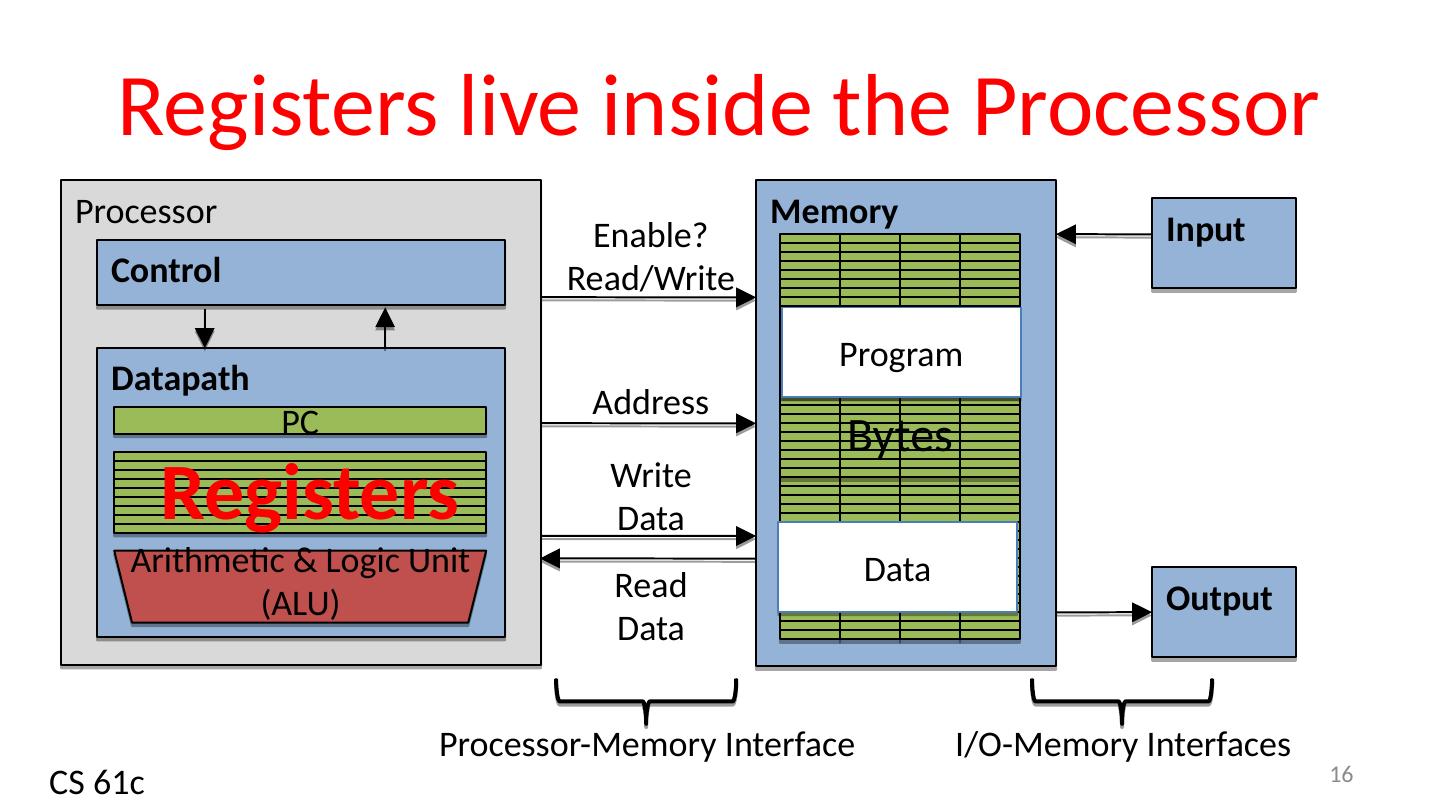

16 .Processor Control Datapath Registers live inside the Processor 16 PC Registers Arithmetic & Logic Unit (ALU) Memory Input Output Bytes Enable? Read/Write Address Write Data ReadData Processor-Memory Interface I/O-Memory Interfaces Program Data CS 61c

17 .Number of RISC-V Registers Drawback : Since registers are in hardware, there are a limited number of them Solution: RISC-V code must be carefully written to efficiently use registers 32 registers in RISC-V, referred to by number x0 – x31 Registers are also given symbolic names, described later Why 32? Smaller is faster, but too small is bad. Goldilocks principle (“This porridge is too hot; This porridge is too cold; this porridge is just right”) Each RISC-V register is 32 bits wide ( RV32 variant of RISC -V ISA) Groups of 32 bits called a word in RISC-V ISA P&H CoD textbook uses the 64-bit variant RV64 (explain differences later) x0 is special, always holds value zero So really only 31 registers able to hold variable values 9/7/17 17

18 .C, Java Variables vs. Registers In C (and most HLLs): V ariables declared and given a type Example: int fahr , celsius ; char a, b, c, d, e; Each variable can ONLY represent a value of the type it was declared (e.g., cannot mix and match int and char variables ) In Assembly Language: R egisters have no type ; O peration determines how register contents are interpreted 9/7/17 18

19 .Outline Assembly Language RISC-V Architecture Registers vs. Variables RISC-V Instructions C-to-RISC-V Patterns And in Conclusion … 9/7/17 19

20 .RISC-V Instruction Assembly Syntax Instructions have an opcode and operands E.g., add x1, x2, x3 # x1 = x2 + x3 9/7/17 20 Operation code ( opcode ) Destination register Second operand register First operand register # is assembly comment syntax

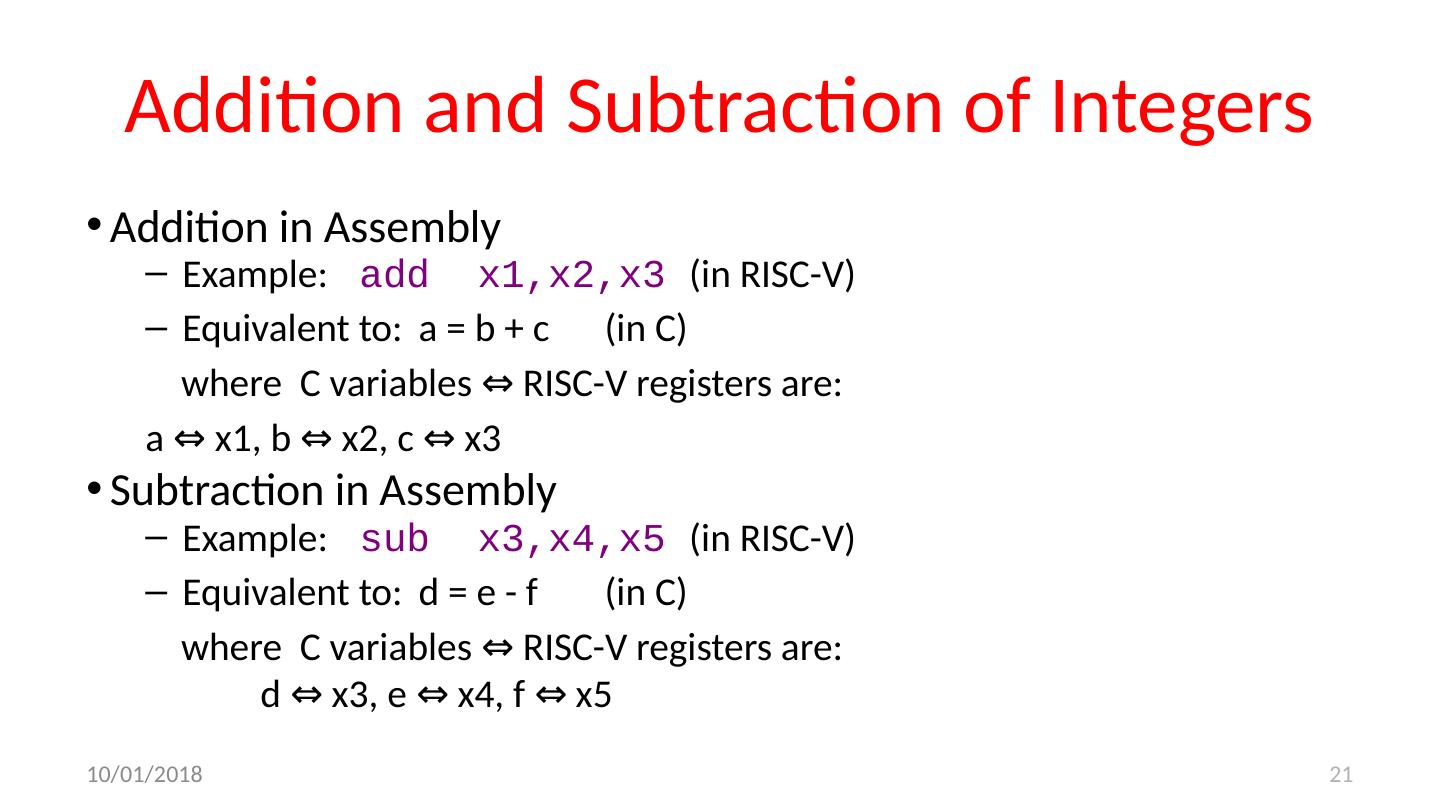

21 .Addition and Subtraction of Integers Addition in Assembly Example: add x1,x2,x3 ( in RISC-V) Equivalent to: a = b + c ( in C) where C variables ⇔ RISC-V registers are: a ⇔ x1, b ⇔ x2, c ⇔ x3 Subtraction in Assembly Example: sub x3,x4,x5 ( in RISC-V) Equivalent to: d = e - f ( in C) where C variables ⇔ RISC-V registers are: d ⇔ x3, e ⇔ x 4 , f ⇔ x 5 9/7/17 21

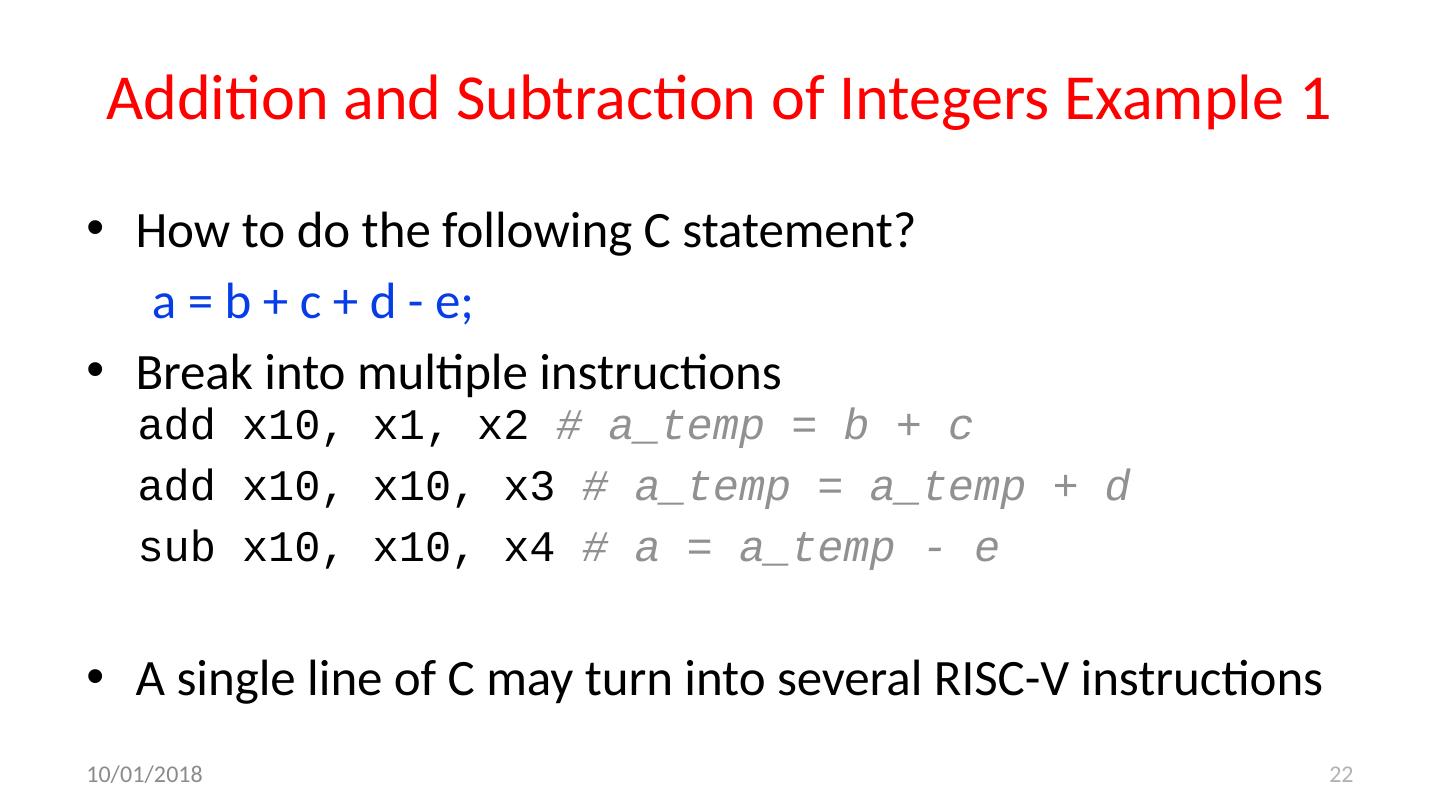

22 .Addition and Subtraction of Integers Example 1 H ow to do the following C statement? a = b + c + d - e; Break into multiple instructions a dd x10 , x1, x2 # a_temp = b + c a dd x10 , x10 , x 3 # a_temp = a_temp + d s ub x10 , x10 , x 4 # a = a_temp - e A single line of C may turn into several RISC-V instructions 9/7/17 22

23 .Immediates Immediates are numerical constants They appear often in code, so there are special instructions for them Add Immediate: addi x3,x4,-10 ( in RISC-V) f = g - 10 ( in C) where RISC-V registers x3,x4 are associated with C variables f, g Syntax similar to add instruction, except that last argument is a number instead of a register add x3,x4, x0 ( in RISC-V) f = g ( in C) 9/7/17 23

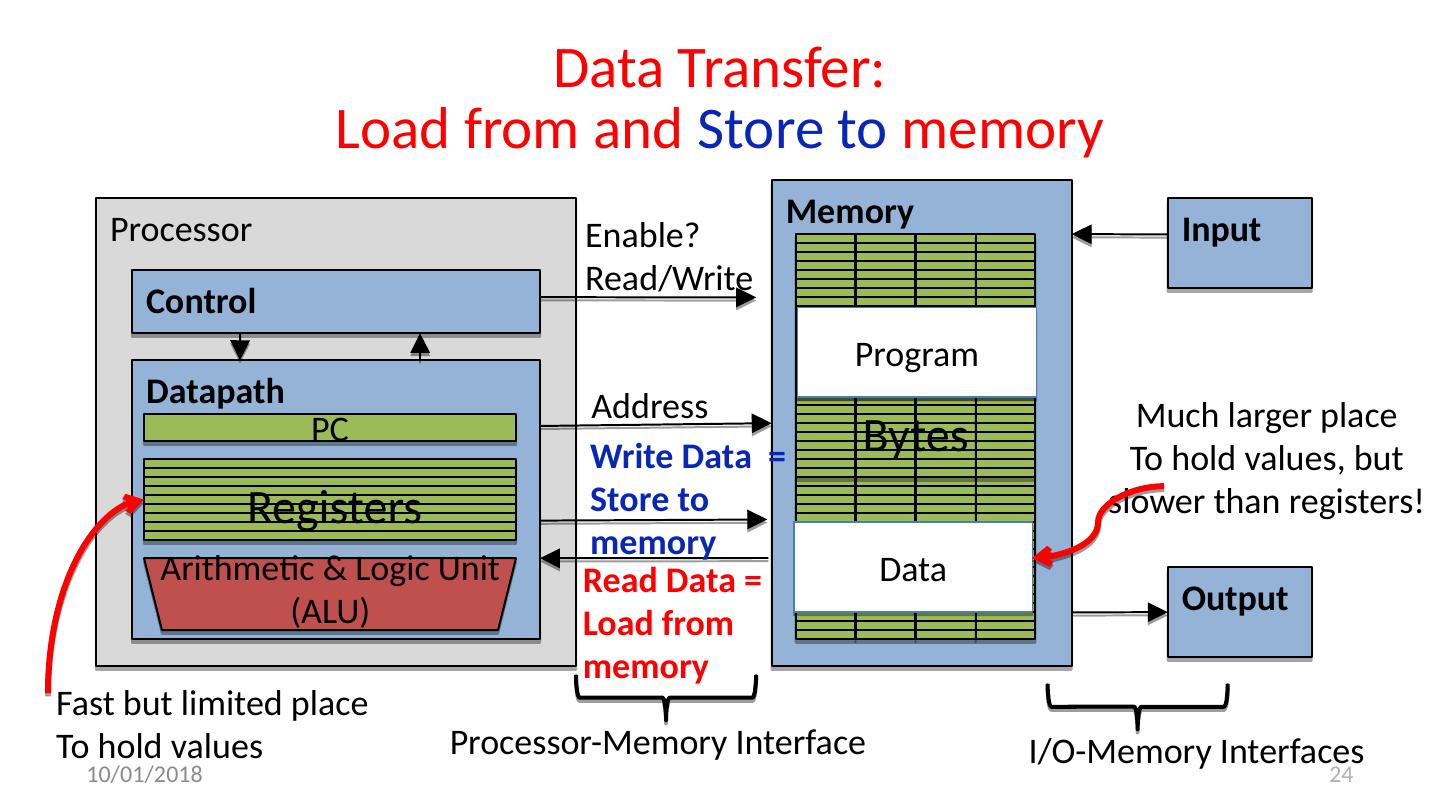

24 .Processor Control Datapath Data Transfer: Load from and Store to memory PC Registers Arithmetic & Logic Unit (ALU) Memory Input Output Bytes Enable? Read/Write Address Write Data = Store to memory Read Data = Load from memory Processor-Memory Interface I/O-Memory Interfaces Program Data 9/7/17 24 Much larger place To hold values, but slower than registers! Fast but limited place To hold values

25 .0 1 2 3 … Memory Addresses are in Bytes D ata typically smaller than 32 bits, but rarely smaller than 8 bits (e.g., char type)–works fine if everything is a multiple of 8 bits 8 bit chunk is called a byte (1 word = 4 bytes) Memory addresses are really in bytes , not words Word addresses are 4 bytes apart Word address is same as address of rightmost byte – least-significant byte (i.e. Little-endian convention) 9/7/17 25 Least-significant byte in a word 0 4 8 12 … 1 5 9 13 … 2 6 10 14 … 3 7 11 15 … 31 24 23 16 15 8 7 0 Least-significant byte gets the smallest address

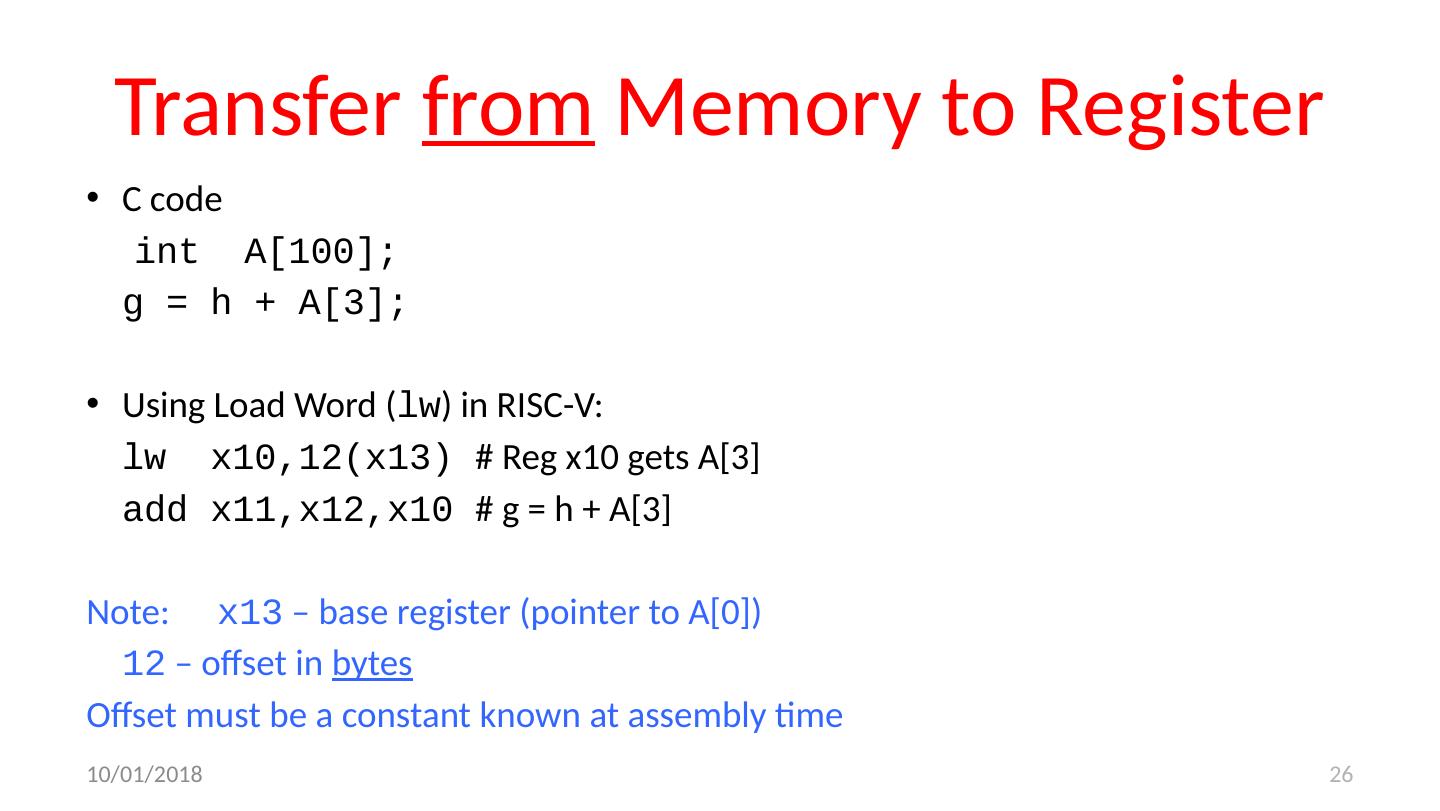

26 .Transfer from Memory to Register C code int A[100]; g = h + A[3]; Using Load Word ( lw ) in RISC-V: lw x10,12(x13) # Reg x10 gets A[3] add x11,x12,x10 # g = h + A[3] Note: x13 – base register (pointer to A[0]) 12 – offset in bytes Offset must be a constant known at assembly time 9/7/17 26

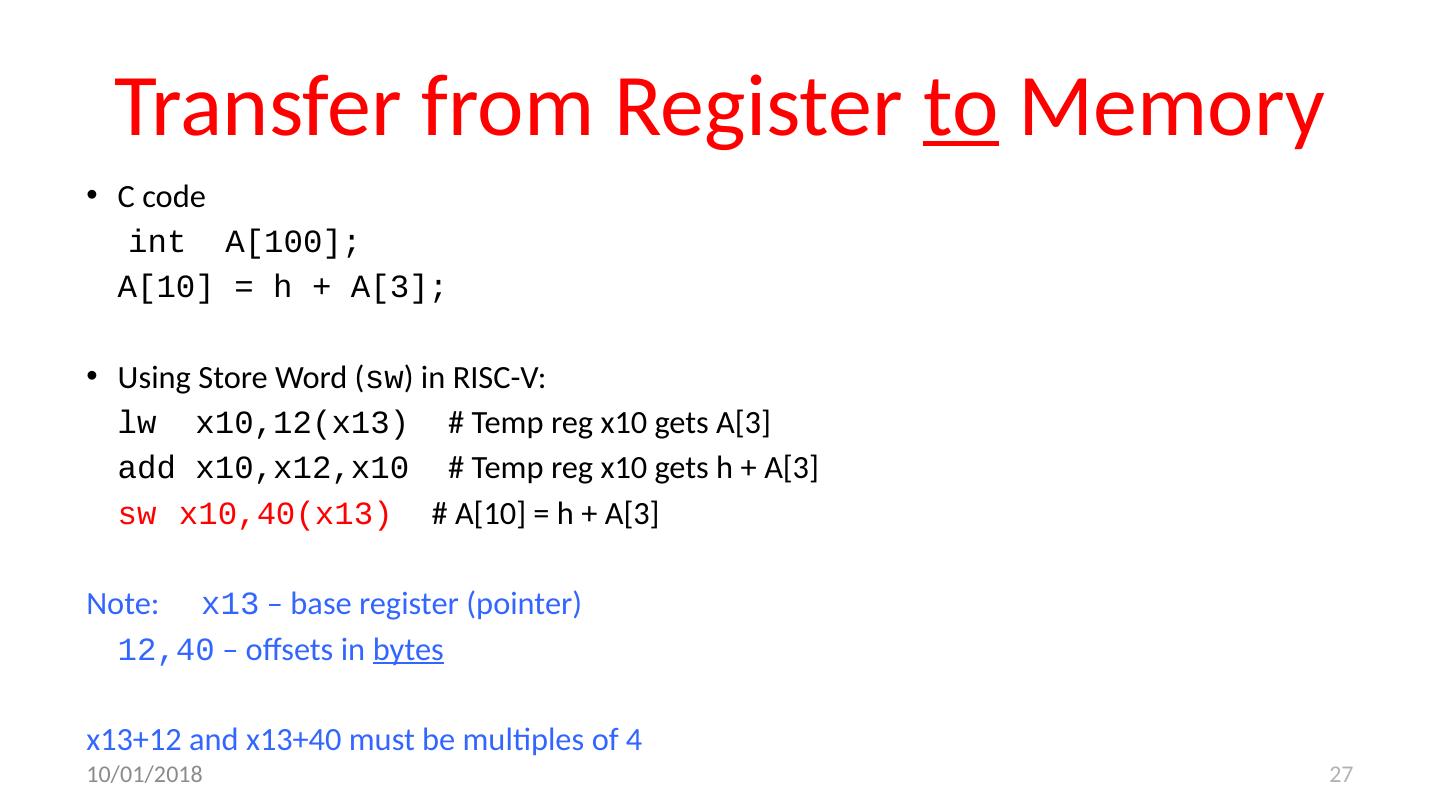

27 .Transfer from Register to Memory C code int A[100]; A[10] = h + A[3]; Using Store Word ( s w ) in RISC-V: lw x10,12(x13) # Temp reg x10 gets A[3] add x10,x12,x10 # Temp reg x10 gets h + A[3] sw x10,40(x13) # A[10] = h + A[3] Note: x13 – base register (pointer) 12,40 – offsets in bytes x13+12 and x13+40 must be multiples of 4 9/7/17 27

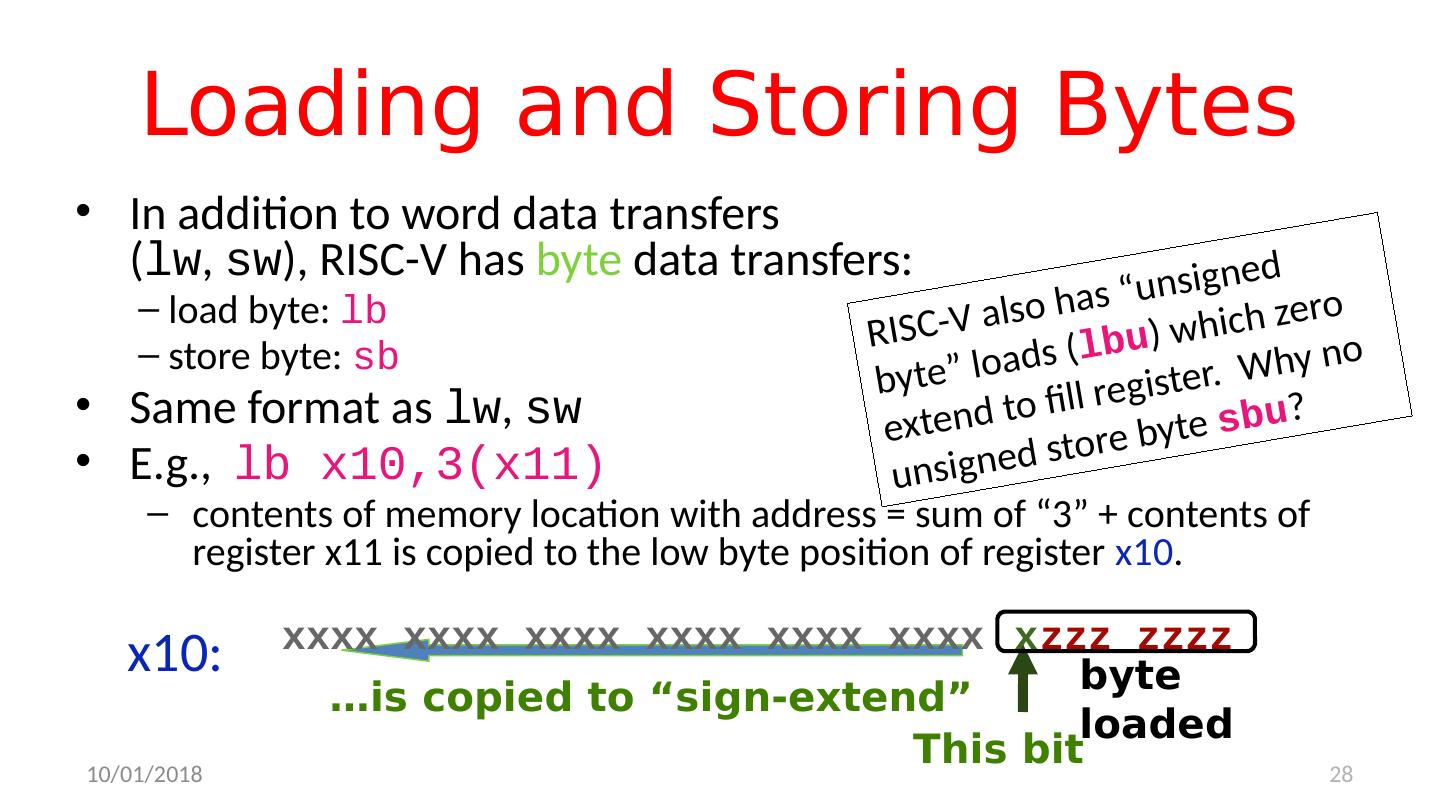

28 .Loading and Storing Bytes In addition to word data transfers ( lw , sw ), RISC-V has byte data transfers: load byte: lb store byte: sb Same format as lw , sw E.g ., lb x10,3(x11) contents of memory location with address = sum of “3” + contents of register x1 1 is copied to the low byte position of register x1 0 . 28 byte loaded zzz zzzz x …is copied to “sign-extend” This bit xxxx xxxx xxxx xxxx xxxx xxxx x10: 9/7/17 RISC-V also has “unsigned byte” loads ( lbu ) which zero extend to fill register. Why no unsigned store byte sbu ?

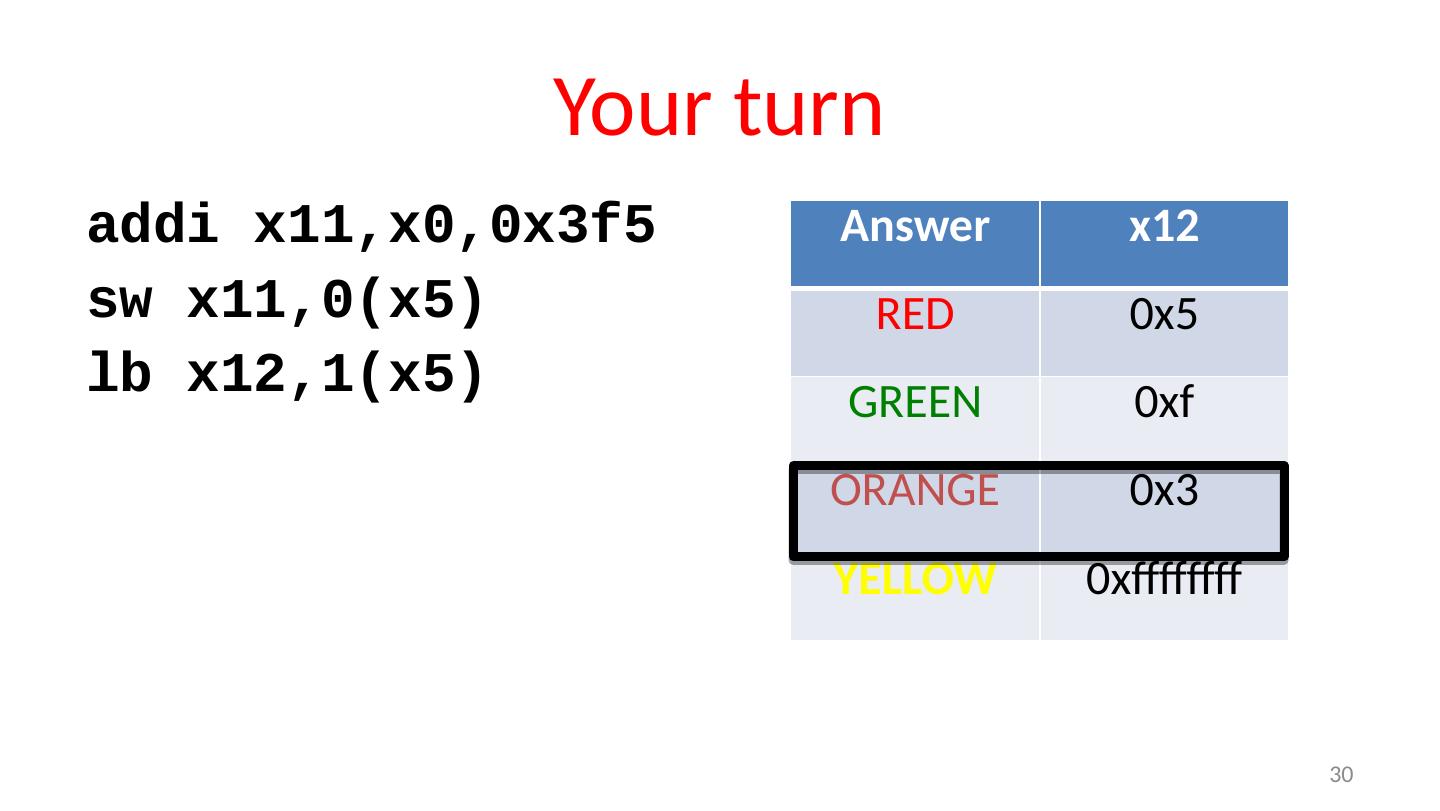

29 .Your turn 29 Answer x12 RED 0x5 GREEN 0xf ORANGE 0x3 YELLOW 0xffffffff addi x11,x0,0x3f5 sw x11,0(x5) lb x12,1(x5)