- 快召唤伙伴们来围观吧

- 微博 QQ QQ空间 贴吧

- 文档嵌入链接

- 复制

- 微信扫一扫分享

- 已成功复制到剪贴板

23 计算机组成--奔腾家族

展开查看详情

1 . Pentium Family CISC architecture – executes IA-32 instruction set Year Processor Clock L1cache L2 cache KB KB 1993 Pentium 233-300 MHz 1995 Pentium Pro 100-200 MHz 8+8 256+1024 1998 Pentium II 233-450 MHz 16+16 256 + 512 (MMX added) 1999 Pentium II Xeon 400-450 MHz 16+16 512 + 2048 1999 Celeron 500-900 MHz 16+16 128 1999 Pentium III 450-1100 16+16 256+512 (70 new MMX MHz instructions) 2000 Pentium III 16+16 1024+2048 2001 Xeon 700-900 MHz 8+8 256+512 Pentium 4 1.3 – 2.1 GHz (NetBurst) All Intel processors are backward compatible.

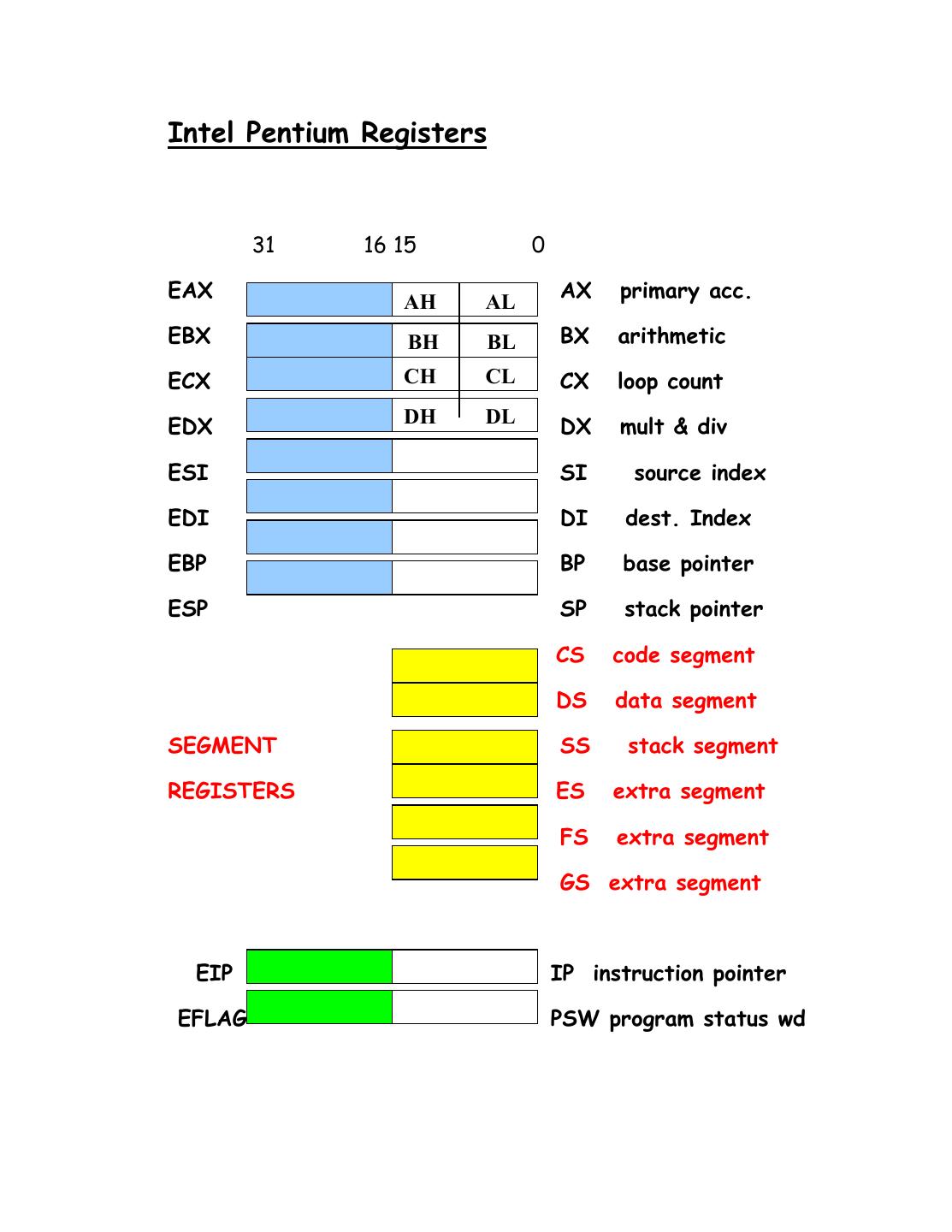

2 .Intel Pentium Registers 31 16 15 0 EAX AX primary acc. AH AL EBX BH BL BX arithmetic ECX CH CL CX loop count EDX DH DL DX mult & div ESI SI source index EDI DI dest. Index EBP BP base pointer ESP SP stack pointer CS code segment DS data segment SEGMENT SS stack segment REGISTERS ES extra segment FS extra segment GS extra segment EIP IP instruction pointer EFLAG PSW program status wd

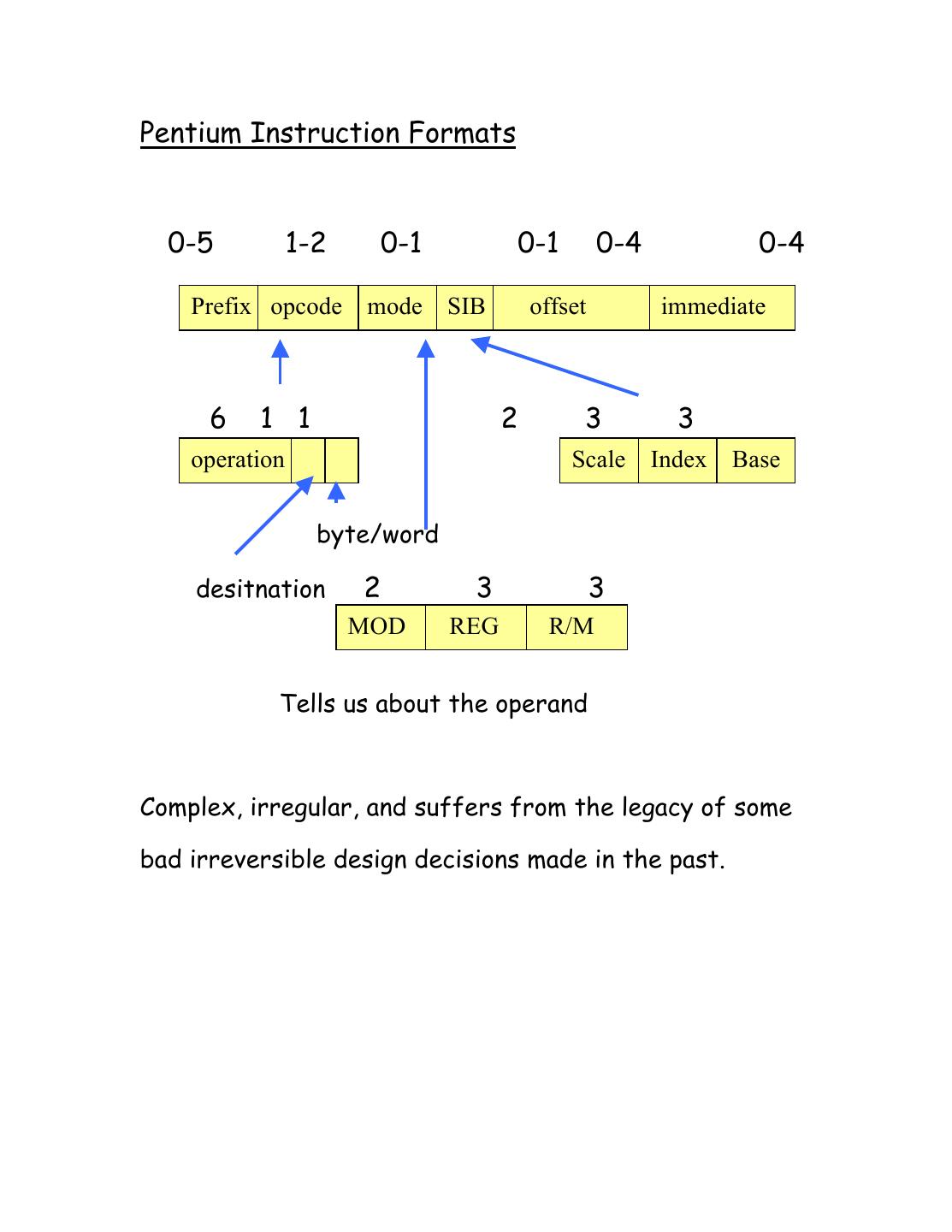

3 .Pentium Instruction Formats 0-5 1-2 0-1 0-1 0-4 0-4 Prefix opcode mode SIB offset immediate 6 1 1 2 3 3 operation Scale Index Base byte/word desitnation 2 3 3 MOD REG R/M Tells us about the operand Complex, irregular, and suffers from the legacy of some bad irreversible design decisions made in the past.

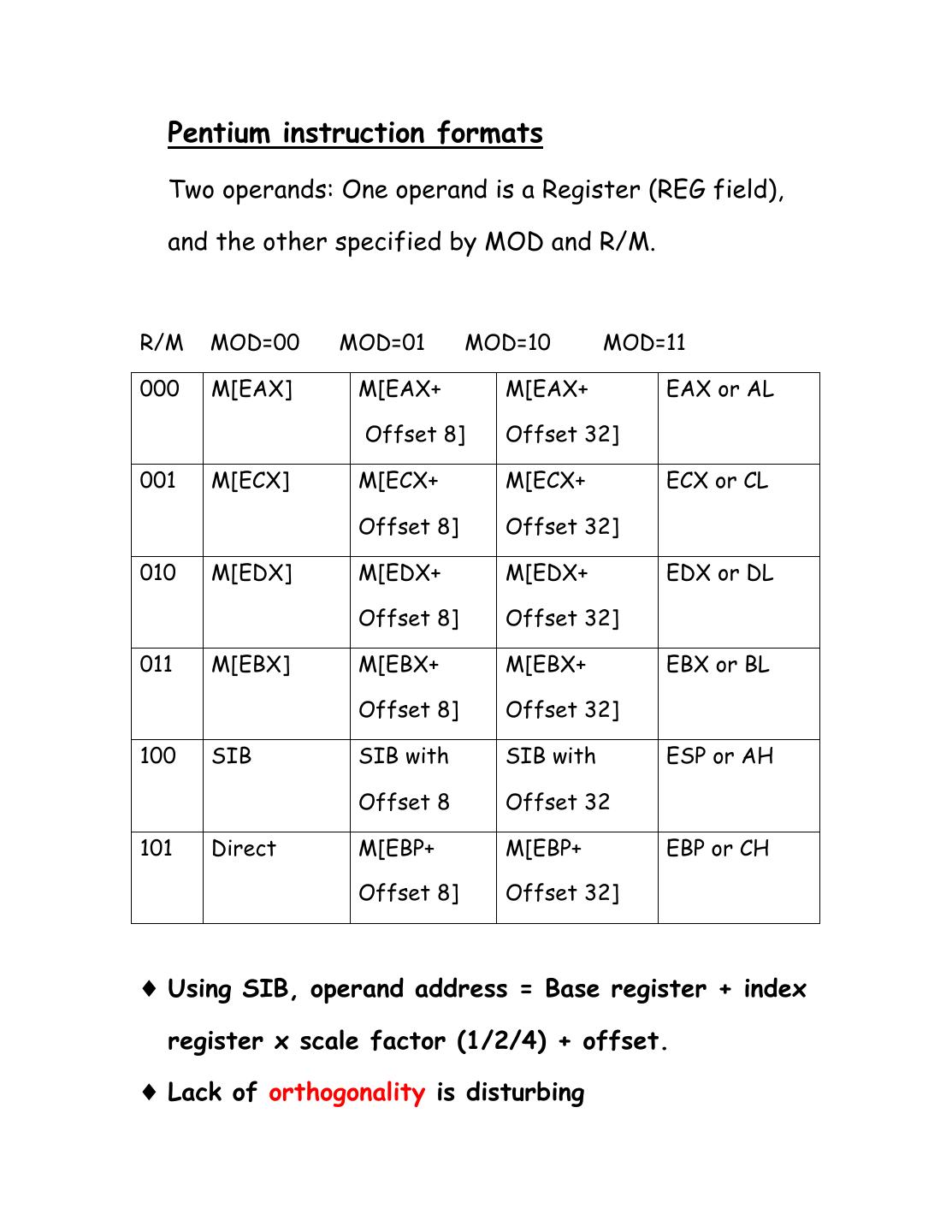

4 . Pentium instruction formats Two operands: One operand is a Register (REG field), and the other specified by MOD and R/M. R/M MOD=00 MOD=01 MOD=10 MOD=11 000 M[EAX] M[EAX+ M[EAX+ EAX or AL Offset 8] Offset 32] 001 M[ECX] M[ECX+ M[ECX+ ECX or CL Offset 8] Offset 32] 010 M[EDX] M[EDX+ M[EDX+ EDX or DL Offset 8] Offset 32] 011 M[EBX] M[EBX+ M[EBX+ EBX or BL Offset 8] Offset 32] 100 SIB SIB with SIB with ESP or AH Offset 8 Offset 32 101 Direct M[EBP+ M[EBP+ EBP or CH Offset 8] Offset 32] ! Using SIB, operand address = Base register + index register x scale factor (1/2/4) + offset. ! Lack of orthogonality is disturbing

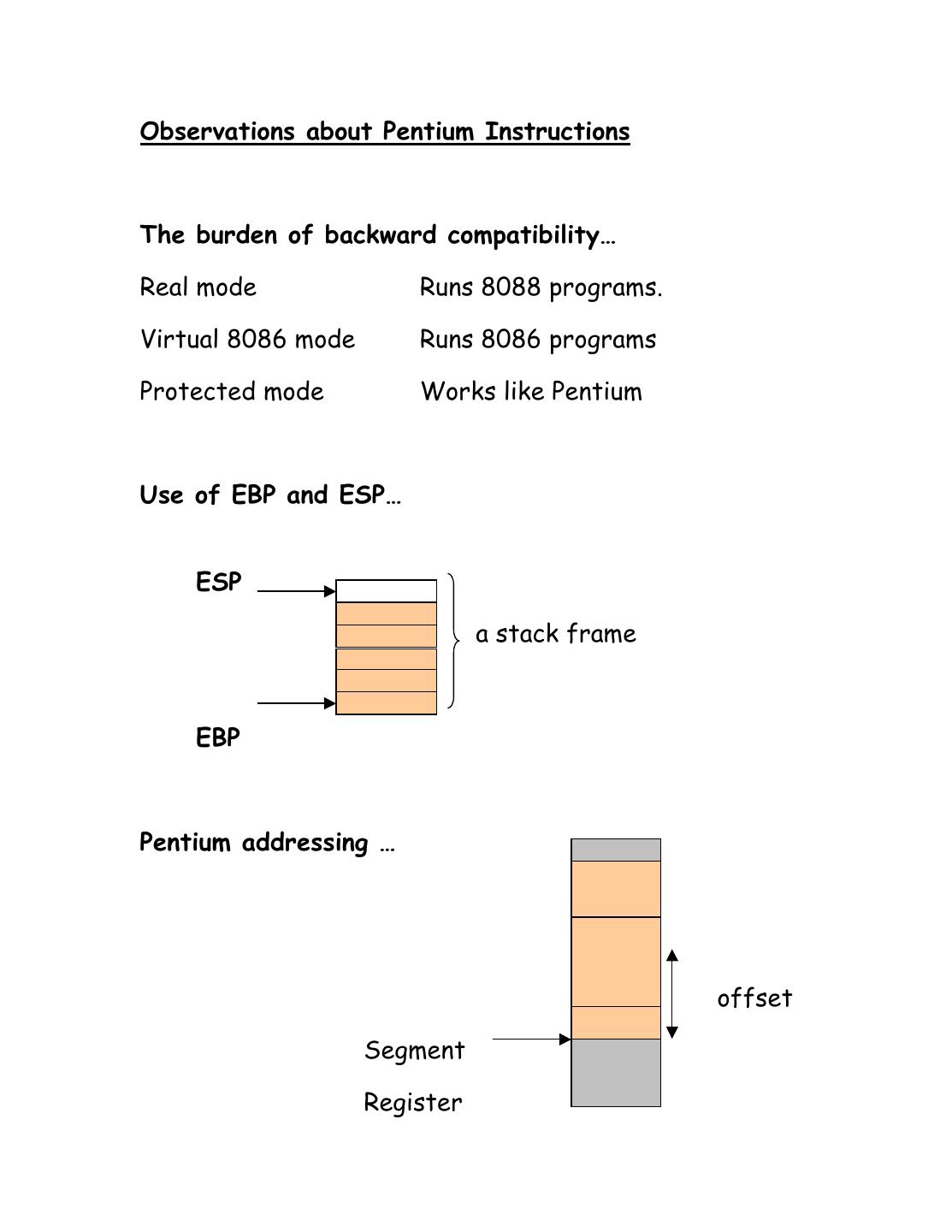

5 .Observations about Pentium Instructions The burden of backward compatibility… Real mode Runs 8088 programs. Virtual 8086 mode Runs 8086 programs Protected mode Works like Pentium Use of EBP and ESP… ESP a stack frame EBP Pentium addressing … offset Segment Register

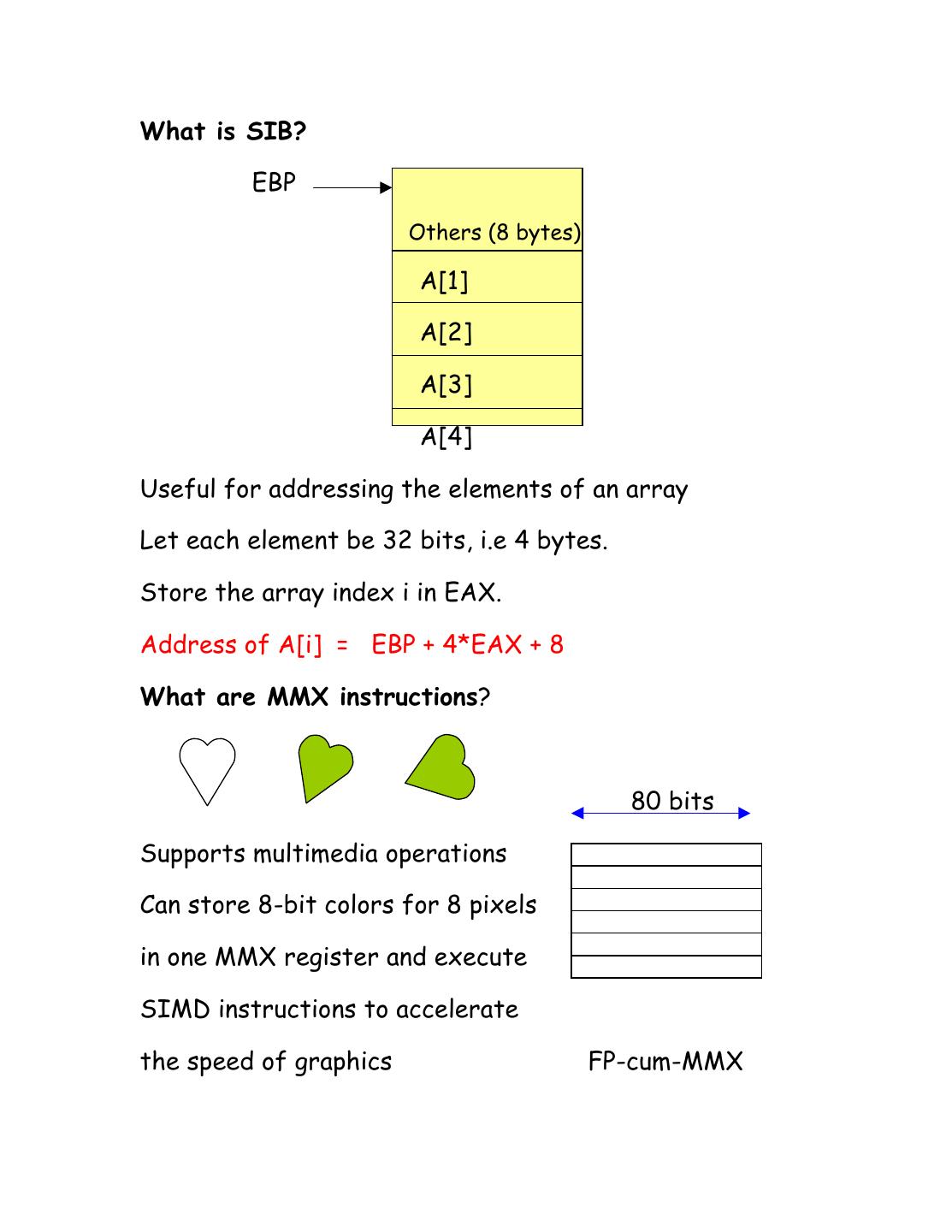

6 .What is SIB? EBP Others (8 bytes) A[1] A[2] A[3] A[4] Useful for addressing the elements of an array Let each element be 32 bits, i.e 4 bytes. Store the array index i in EAX. Address of A[i] = EBP + 4*EAX + 8 What are MMX instructions? 80 bits Supports multimedia operations Can store 8-bit colors for 8 pixels in one MMX register and execute SIMD instructions to accelerate the speed of graphics FP-cum-MMX

7 .What are Prefix bytes? Attributes to instructions… REP "instruction# Repeat the instruction until ECX=0 REPZ "instruction# Repeat the instruction until Z-flag is set. LOCK "instruction# Lock the memory bus until the instruction execution is complete.

8 .Case Study : Design of Pentium Pro µop 1 µop 2 µop 3 Instruction 1 µop 1 Instruction 2 Instruction 3 µop 1 µop 2 µop 3 µop 4 Instruction 4 µop 1 µop 2 Instruction 5 ! Each instruction is converted into a sequence of µops that are RISC like instructions. This makes the pipeline much deeper and branch penalty increases. ! Uses a 512-entry 2-level branch predictor

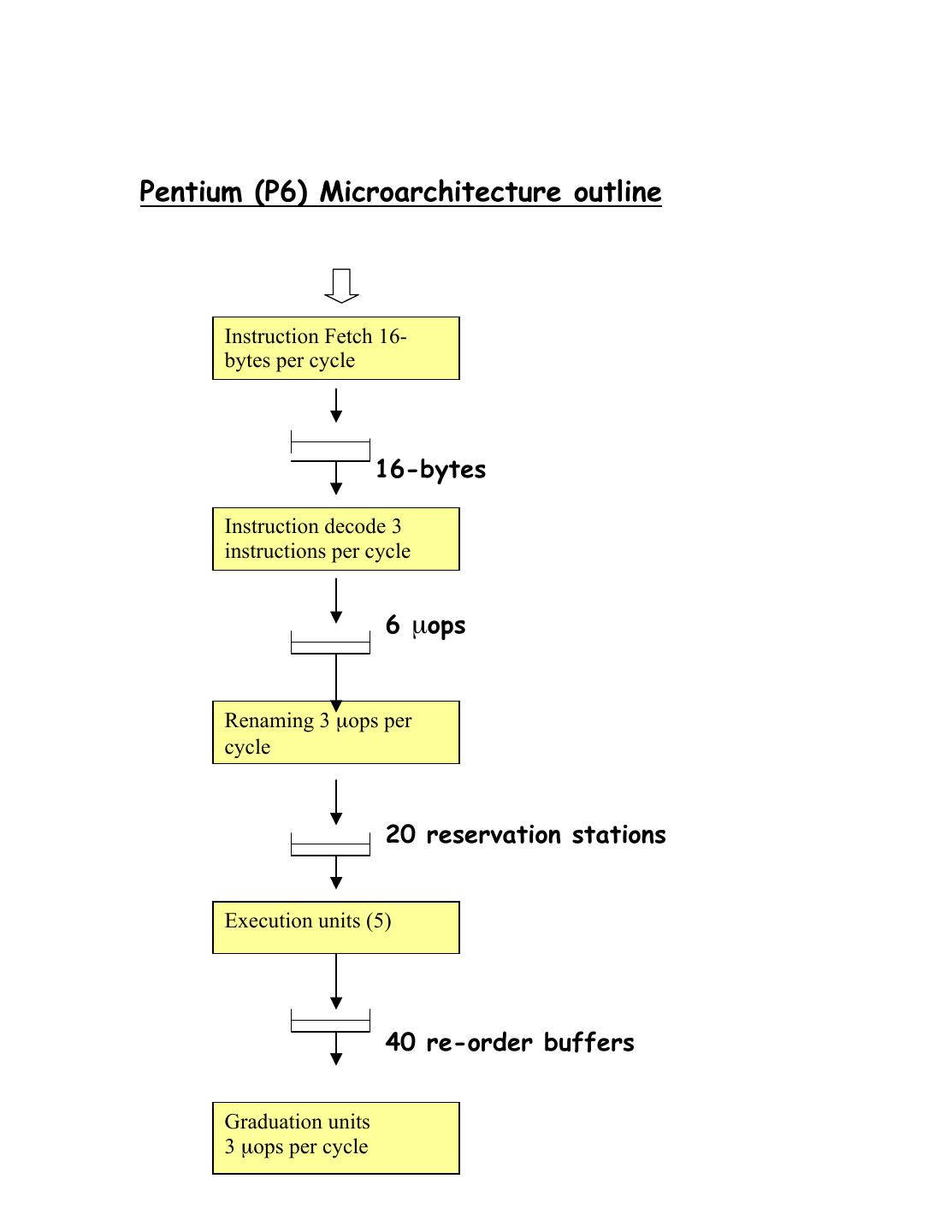

9 .Pentium (P6) Microarchitecture outline Instruction Fetch 16- bytes per cycle 16-bytes Instruction decode 3 instructions per cycle 6 µops Renaming 3 µops per cycle 20 reservation stations Execution units (5) 40 re-order buffers Graduation units 3 µops per cycle

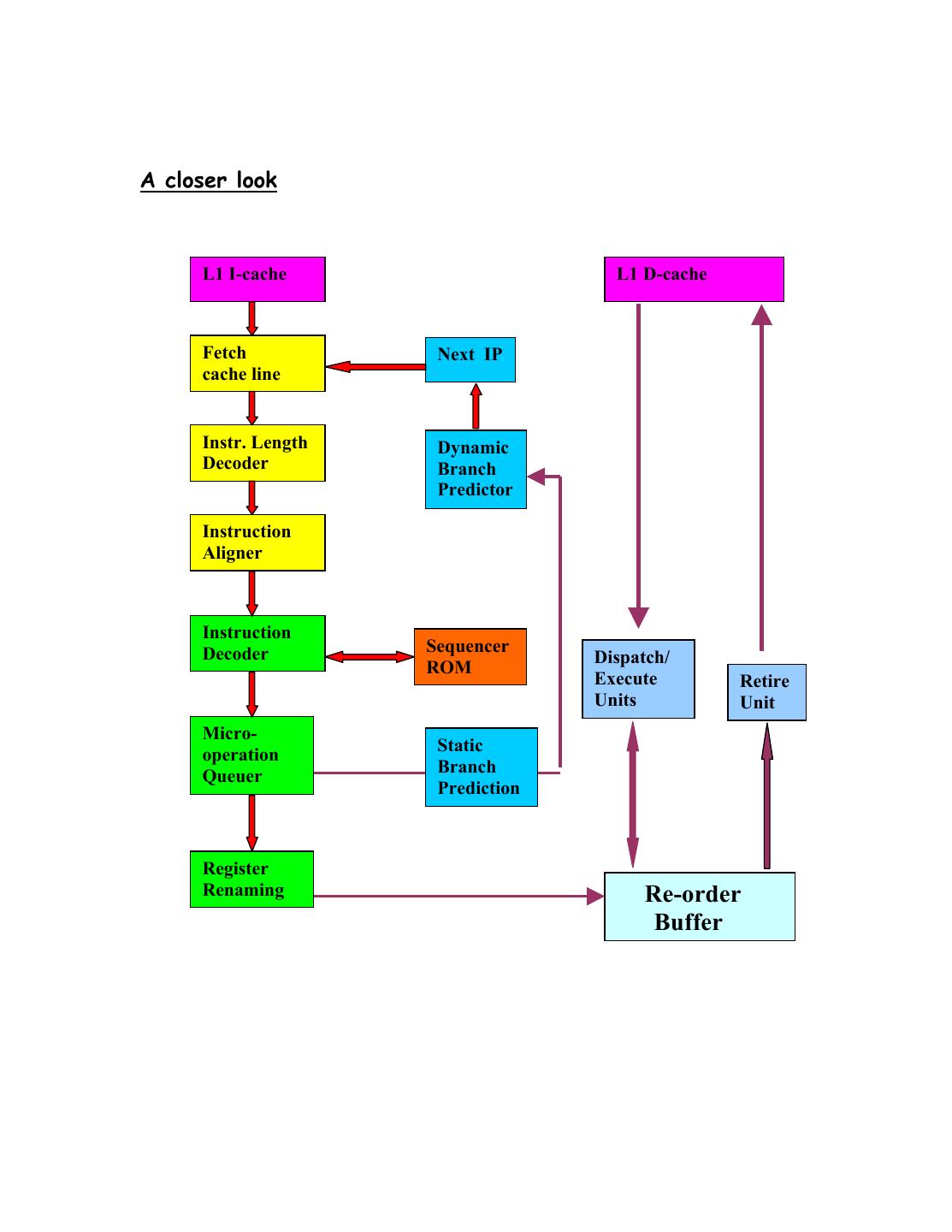

10 .A closer look L1 I-cache L1 D-cache Fetch Next IP cache line Instr. Length Dynamic Decoder Branch Predictor Instruction Aligner Instruction Decoder Sequencer Dispatch/ ROM Execute Retire Units Unit Micro- operation Static Branch Queuer Prediction Register Renaming Re-order Buffer

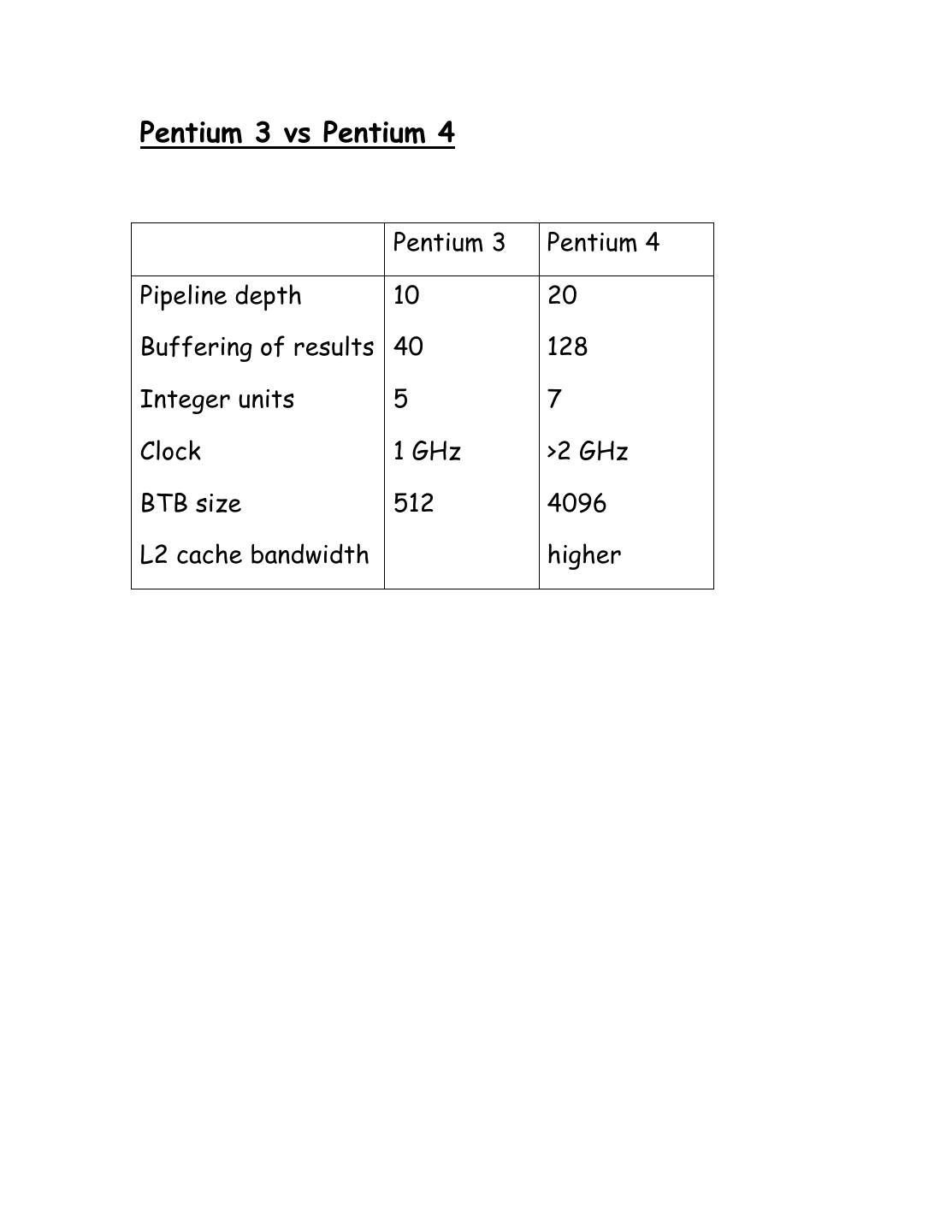

11 .Pentium 3 vs Pentium 4 Pentium 3 Pentium 4 Pipeline depth 10 20 Buffering of results 40 128 Integer units 5 7 Clock 1 GHz >2 GHz BTB size 512 4096 L2 cache bandwidth higher