- 快召唤伙伴们来围观吧

- 微博 QQ QQ空间 贴吧

- 文档嵌入链接

- 复制

- 微信扫一扫分享

- 已成功复制到剪贴板

11 计算机组成--逻辑电路设计

展开查看详情

1 .Logic Design (continued) XOR Revisited XOR is also called modulo-2 addition. A B C F 0 0 0 0 A ⊕ B = 1 only when there are an 0 0 1 1 odd number of 1’s in (A,B). The 0 1 0 1 same is true for A ⊕ B ⊕ C also. 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 0 1 1 1 1 1 ⊕A=A Why? 0⊕A=A

2 .Logic Design Examples Half Adder A B S C A Half Sum (S) 0 0 0 0 Adder B Carry (C) 0 1 1 0 1 0 1 0 S=A B 1 1 0 1 C = A.B A Carry B Sum

3 . Full Adder Sum (S) A B Cin S Cout A Full 0 0 0 0 0 Adder B 0 0 1 1 0 Cin Carry (Cout) 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 S=A B Cin Cout = A.B + B.Cin + A.Cin Design a full adder using two half-adders (and a few gates if necessary) Can you design a 1-bit subtractor?

4 .Decoders n A typical decoder has n inputs and 2 outputs. Enable A B D3 D2 D1 D0 D0 0 0 0 0 0 1 A D1 0 1 0 0 1 0 B D2 1 0 0 1 0 0 D3 1 1 1 0 0 0 A 2-to-4 decoder and its truth table D3 = A.B Draw the circuit of this decoder. D2 = A.B D1 = A.B The decoder works per specs D0 = A.B when (Enable = 1). When Enable = 0, all the outputs are 0. Exercise. Design a 3-to-8 decoder. Question. Where are decoders used? Can you design a 2-4 decoder using 1-2 decoders?

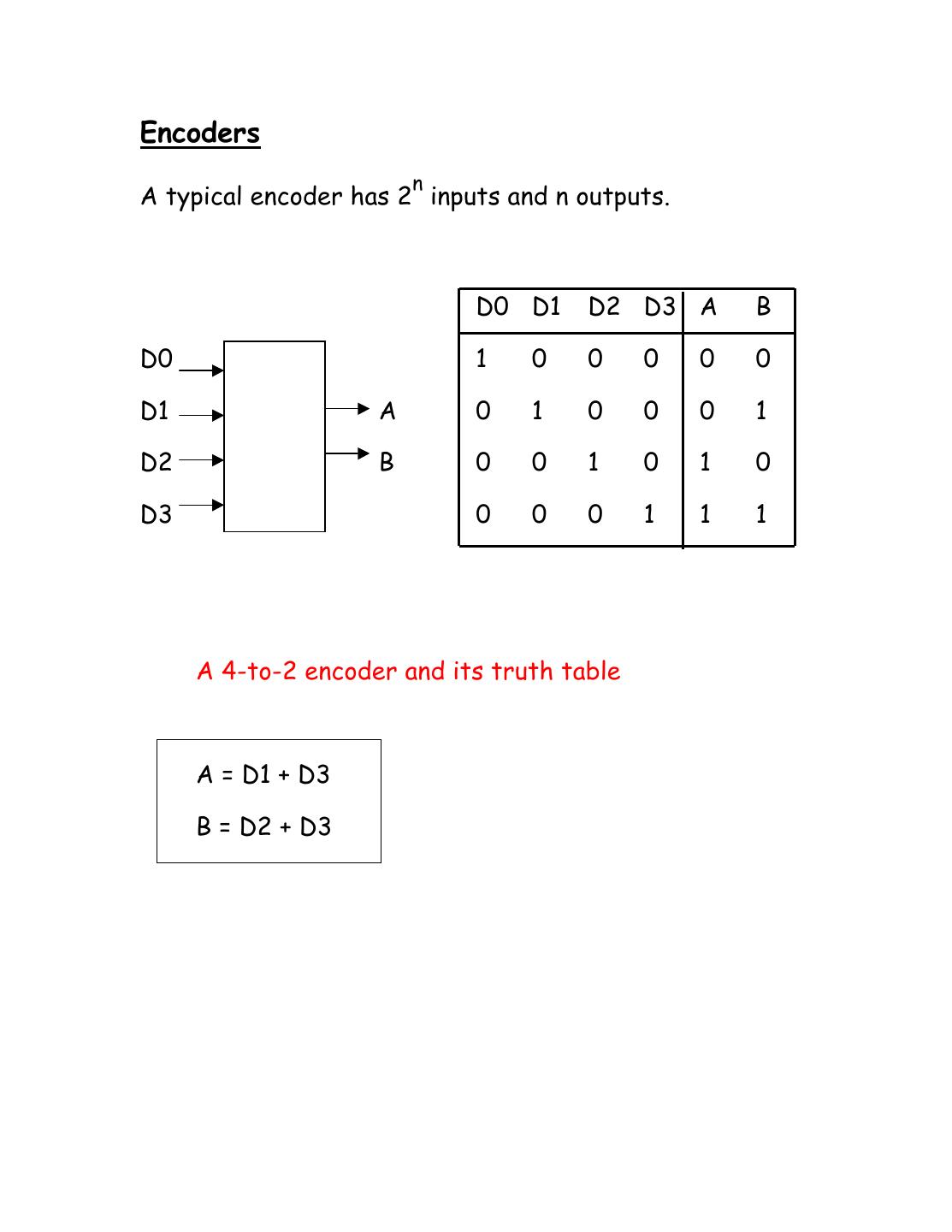

5 .Encoders n A typical encoder has 2 inputs and n outputs. D0 D1 D2 D3 A B D0 1 0 0 0 0 0 D1 A 0 1 0 0 0 1 D2 B 0 0 1 0 1 0 D3 0 0 0 1 1 1 A 4-to-2 encoder and its truth table A = D1 + D3 B = D2 + D3

6 .Multiplexor It is a many-to-one switch, also called a selector. A 0 F S = 0, F = A B 1 S = 1, F = B Control S Specifications of the mux A 2-to-1 mux F = S. A + S. B Exercise. Design a 4-to-1 multiplexor using two 2-to- 1 multiplexors.

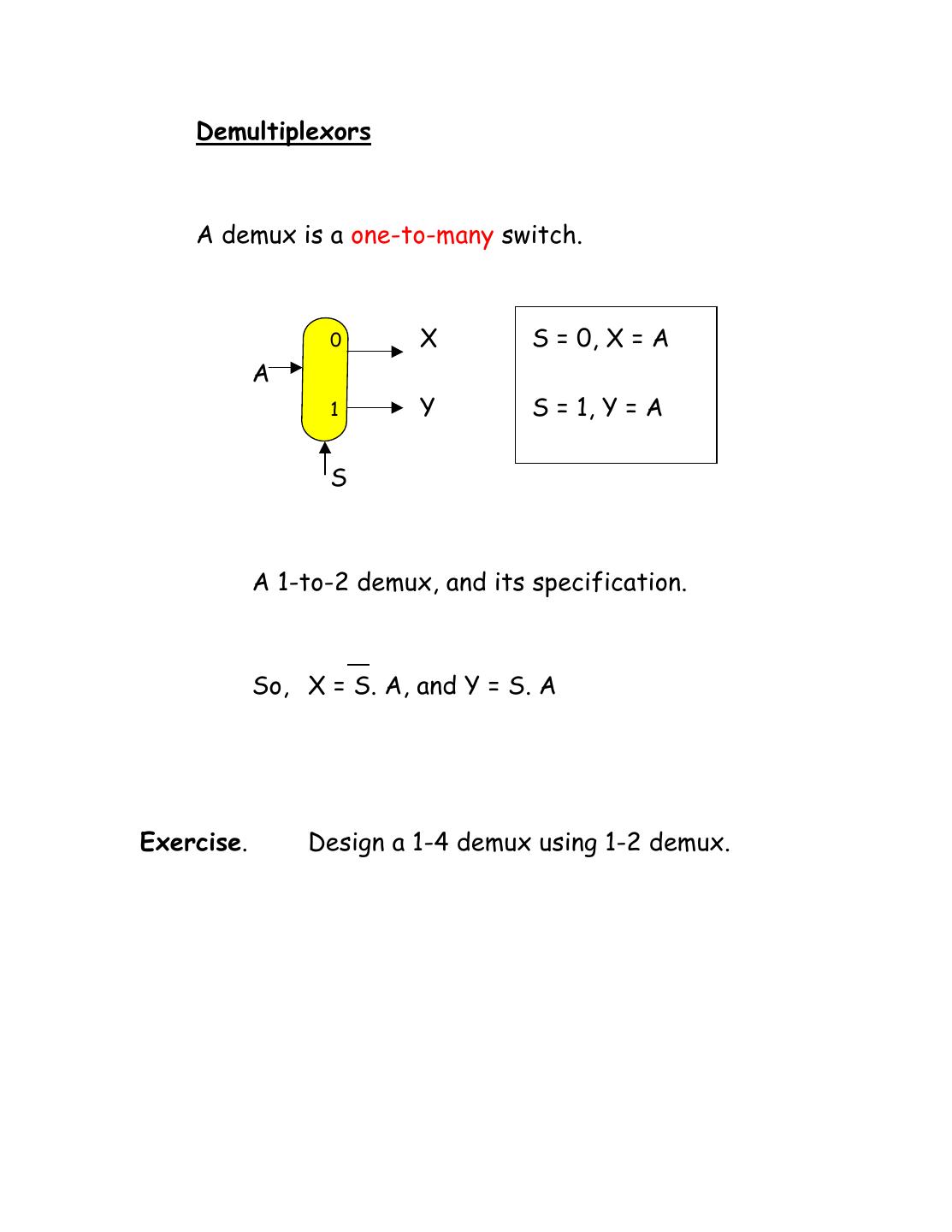

7 . Demultiplexors A demux is a one-to-many switch. 0 X S = 0, X = A A 1 Y S = 1, Y = A S A 1-to-2 demux, and its specification. So, X = S. A, and Y = S. A Exercise. Design a 1-4 demux using 1-2 demux.